### UNIVERSIDADE FEDERAL DO PARANÁ

### ALINE SANTANA CORDEIRO

# PORTING MACHINE LEARNING ALGORITHMS TO VECTOR-IN-MEMORY ARCHITECTURE

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre em Informática no Programa de Pós-Graduação em Informática, Setor de Ciências Exatas, da Universidade Federal do Paraná.

Área de concentração: Ciência da Computação.

Orientador: Prof. Dr. Marco Antonio Zanata Alves.

### CURITIBA PR

2020

## Catalogação na Fonte: Sistema de Bibliotecas, UFPR Biblioteca de Ciência e Tecnologia

| C794p | Cordeiro, Aline Santana<br>Porting machine learning algorithms to vector-in-memory architecture [recurso<br>eletrônico] / Aline Santana Cordeiro. – Curitiba, 2020.                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                 |

|       | Dissertação - Universidade Federal do Paraná, Setor de Ciências Exatas, Programa de Pós-<br>Graduação em Informática, 2020.                                                                     |

|       | Orientador: Marco Antonio Zanata Alves.                                                                                                                                                         |

|       |                                                                                                                                                                                                 |

|       | <ol> <li>Aprendizado do computador. 2. Algoritmos. 3. Sistemas de memória de computadores.</li> <li>I. Universidade Federal do Paraná. II. Alves, Marco Antonio Zanata. III. Título.</li> </ol> |

|       | CDD: 006.32                                                                                                                                                                                     |

|       |                                                                                                                                                                                                 |

|       |                                                                                                                                                                                                 |

Bibliotecária: Vanusa Maciel CRB- 9/1928

MINISTÉRIO DA EDUCAÇÃO SETOR DE CIENCIAS EXATAS UNIVERSIDADE FEDERAL DO PARANÁ PRÓ-REITORIA DE PESQUISA E PÓS-GRADUAÇÃO PROGRAMA DE PÓS-GRADUAÇÃO INFORMÁTICA -40001016034P5

### **TERMO DE APROVAÇÃO**

Os membros da Banca Examinadora designada pelo Colegiado do Programa de Pós-Graduação em INFORMÁTICA da Universidade Federal do Paraná foram convocados para realizar a arguição da dissertação de Mestrado de ALINE SANTANA CORDEIRO intitulada: Porting Machine Learning Algorithms to Vector-in-Memory Architecture, sob orientação do Prof. Dr. MARCO ANTONIO ZANATA ALVES, que após terem inquirido a aluna e realizada a avaliação do trabalho, são de parecer pela sua APROVAÇÃO no rito de defesa.

A outorga do título de mestre está sujeita à homologação pelo colegiado, ao atendimento de todas as indicações e correções solicitadas pela banca e ao pleno atendimento das demandas regimentais do Programa de Pós-Graduação.

CURITIBA, 25 de Novembro de 2020.

Assinatura Eletrônica 25/11/2020 19:58:20.0 MARCO ANTONIO ZANATA ALVES Presidente da Banca Examinadora (UNIVERSIDADE FEDERAL DO PARANÁ)

> Assinatura Eletrônica 30/11/2020 07:50:32.0 LUIS CARLOS ERPEN DE BONA Avaliador Interno (UNIVERSIDADE FEDERAL DO PARANÁ)

> > Assinatura Eletrônica 27/11/2020 10:12:16.0 EDUARDO ROCHA RODRIGUES Avaliador Externo (IBM RESEARCH)

e insira o codigo 63694

#### ACKNOWLEDGEMENTS

After almost 3 years of work and facing a harsh year of pandemic, I would like to thank Capes and Serrapilheira for funding and making possible my research with exclusive dedication during this period.

Likewise, I would like to thank my supervisor, Ph.D. Marco Antonio Zanata Alves, for all the support and guidance since my undergrad. I am very grateful that you have given me the opportunity and encouragement to start and finish this research.

Besides, I would like to acknowledge Ph.D. Paulo Cesar Santos from UFRGS, for his contributions to this dissertation proposal, the support, and discussions at the end of this work.

I also would like to thank all my colleagues from our laboratory, HiPES, who have supported me during this period. Especially MSc. Sairo Raoní dos Santos, who has been working with me on the same project and shared joys and sorrows.

In addition, I would like to thank my companion Rafael, my sister Deyse, my parents, and my friends for all the support and advice. You all have given me the opportunity in many ways of doing and finishing this work.

#### **RESUMO**

A Aprendizagem de Máquina surgiu por volta de 1960, com o foco na capacidade de aprendizagem do computador e, desde então, se tornou uma ferramenta útil para analisar a vasta quantidade de dados que é gerada em todos os campos da ciência nos dias de hoje. Ao longo dos anos, diversos algoritmos foram criados para analisar, reconhecer padrões e fazer previsões a partir de amostras de dados e, simultaneamente, a movimentação de dados dentro de sistemas computacionais ganhou foco devido ao seu alto impacto no tempo de execução e no consumo de energia. Nesse contexto, as arquiteturas de processamento próximo à memória surgiram como uma solução promissora para o processamento massivo de dados, reduzindo drasticamente a movimentação destes. Além das abordagens mais comuns para o problema, como Central Processing Units (CPUs) e Graphic Processing Units (GPUs), também existem abordagens diferentes, como Application Specific Integrated Circuits (ASICs) e Field-Programmable Gate Arrays (FPGAs). Esses aceleradores são opções interessantes para executar algoritmos de aprendizagem de máquina, no entanto, eles ainda apresentam problemas relacionados ao Memory-Wall, pois exigem movimentação de dados fora do chip entre a memória e os dispositivos de processamento e, como as soluções de processamento próximo à memória conectam a unidade de processamento ao dispositivo de armazenamento, elas reduzem os problemas originados pela movimentação de dados. Este trabalho avalia se é possível obter alto desempenho computacional para algoritmos de aprendizagem de máquina usando uma arquitetura de processamento próximo à memória que seja de propósito geral e que executa instruções vetoriais. Assim, é apresentada uma abordagem para executar alguns kernels de inferência como k-Nearest Neighbors (kNN), Multi Layer Perceptron (MLP) e Convolutional Neural Network (CNN) usando a arquitetura de Vetor-em-Memória (VIMA), uma arquitetura de processamento próximo à memória que permite reutilização de dados e redução da latência de execução. A ideia é migrar esses algoritmos de aprendizagem de máquina com a Intrinsics-VIMA, uma biblioteca que emula o cojunto de instruções da VIMA e simula as aplicações usando um simulador orientado a traços para avaliar seu desempenho computacional e o consumo de energia. As contribuições deste trabalho são: (i) uma nova biblioteca Intrinsics que emula o conjunto de instruções da VIMA de forma fácil; (ii) ideias sobre como migrar algoritmos de aprendizagem de máquina usando Intrinsics-VIMA, e; (iii) a avaliação dos resultados dos algoritmos considerando o ambiente de simulação. Os resultados indicam acelerações de até 10× para o kNN, 11× para o MLP e 3× para a convolução ao executá-los na VIMA comparado com uma versão de alto desempenho do x86.

Palavras-chave: memórias inteligentes, processamento próximo à memória, aprendizagem de máquina, arquitetura vetorizada

#### ABSTRACT

Machine Learning (ML) emerged around 1960, focusing on the computer learning capacity. Since then, it became a handy tool to analyze the vast amount of data currently generated in every field of science. For this purpose, several algorithms were created to analyze, recognize patterns, and make predictions from data samples. Simultaneously, data movement inside computer systems gains more focus due to its high impact on time and energy consumption. In this context, the Near-Data Processing (NDP) architectures emerged as a prominent solution to massive data processing by drastically reducing data movement. Besides the most common approaches to the problem, such as Central Processing Units (CPUs) and Graphics Processing Units (GPUs), there are also different approaches, such as Application Specific Integrated Circuits (ASICs) and Field-Programmable Gate Arrays (FPGAs). These accelerators are all exciting options to solve ML algorithms. Nevertheless, they still present problems related to the Memory Wall, as they still requiring off-chip data movement between the memory and the processing devices. As NDP solutions attach the processing unit to the storage device, they mitigate problems originated by data movement. This work evaluates whether it is possible to achieve high computational performance for ML algorithms using a general-purpose NDP architecture that operates on vector instructions. Thus, it presents an approach to execute inference kernels from k-Nearest Neighbors (kNN), Multi Layer Perceptron (MLP), and Convolutional Neural Network (CNN) algorithms using Vector-in-Memory Architecture (VIMA), an NDP architecture that allows data reuse and latency reduction. The idea is to port those ML algorithms with Intrinsics-VIMA. This library emulates VIMA Instruction Set Architecture (ISA), and simulate the applications using a trace-driven simulator to evaluate its computational performance and energy consumption. The contribution of this work are: (i) a new Intrinsics library that emulates VIMA ISA in an easy way; (ii) insights on how to migrate ML algorithms using Intrinsics-VIMA, and; (iii) results evaluation of the algorithms considering the simulation environment indicate speedups up to 10× for KNN, 11× for MLP, and 3× for convolution when executing near-data compared to a high-performance x86 baseline.

Keywords: smart-memories, near-data processing, machine learning, vector architecture

## LIST OF FIGURES

| 2.1  | Block diagram of an 3D-stacked memory                                             | 20 |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | Block diagram of NDP architectures interconnection                                | 20 |

| 2.3  | HMC block diagram with 32 vaults with 16 banks each one                           | 21 |

| 2.4  | Architectural difference between HIVE and VIMA                                    | 22 |

| 2.5  | 3D-stacked memory module with VIMA architecture                                   | 23 |

| 2.6  | Example of x86 assembly replacement                                               | 25 |

| 4.1  | Sequence of steps to simulate an application                                      | 35 |

| 4.2  | Von Neumann neighboring convolution                                               | 37 |

| 4.3  | Moore neighboring convolution                                                     | 37 |

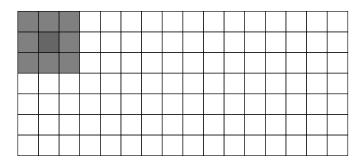

| 4.4  | Instance classification by votes                                                  | 38 |

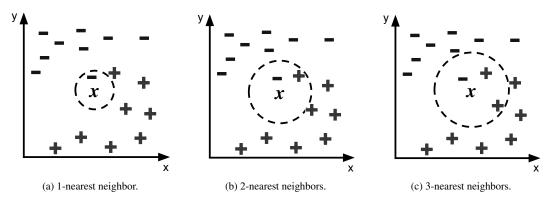

| 4.5  | A neuron representation                                                           | 39 |

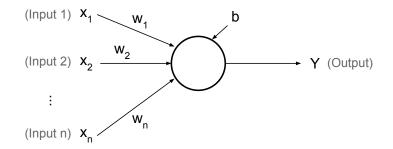

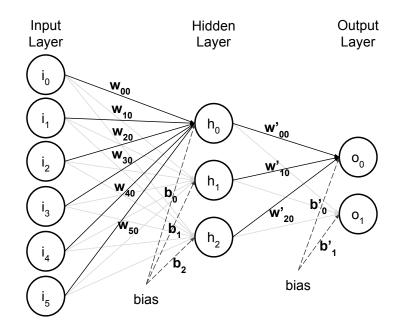

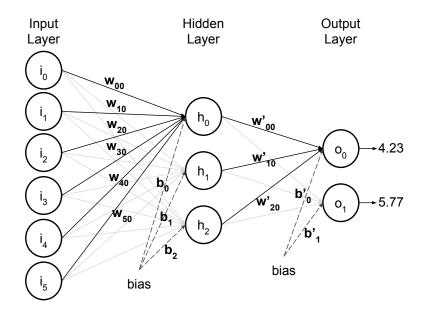

| 4.6  | A representation of a neural network                                              | 39 |

| 4.7  | Neural network output distribution at the beginning of the training               | 40 |

| 4.8  | Moore neighboring convolution                                                     | 42 |

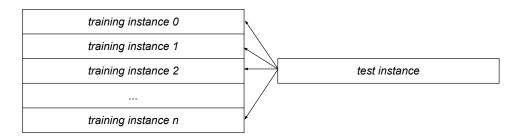

| 4.9  | The whole training dataset has to be available for each test instance             | 42 |

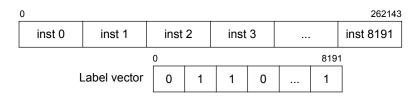

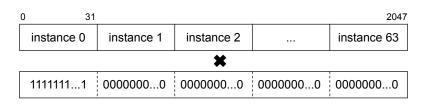

| 4.10 | Full utilization of a VIMA vector for training and test instances                 | 42 |

| 4.11 | VIMA vectors with training instances with 32 features and the respective labels . | 43 |

| 4.12 | Operation to apply a mask over a VIMA vector of 8 KB                              | 43 |

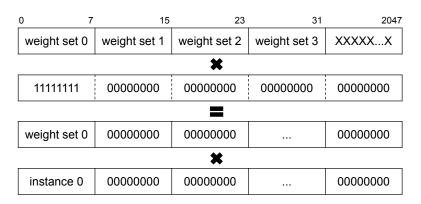

| 4.13 | Example of a multiplication between input layer and sets of weights               | 44 |

| 4.14 | Example of a VIMA vector with four sets of weights                                | 45 |

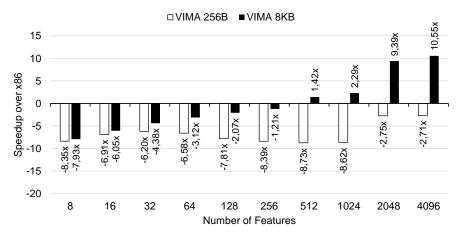

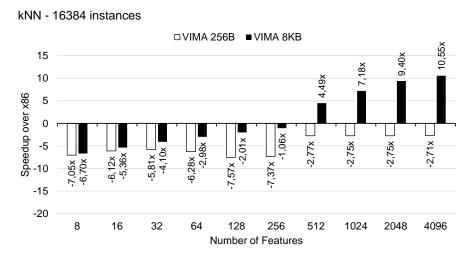

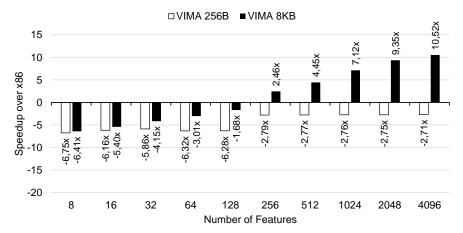

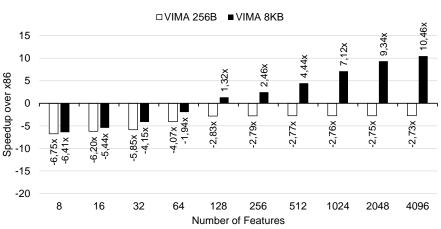

| 5.1  | VIMA's speedup over x86 for kNN with 4096 instances                               | 51 |

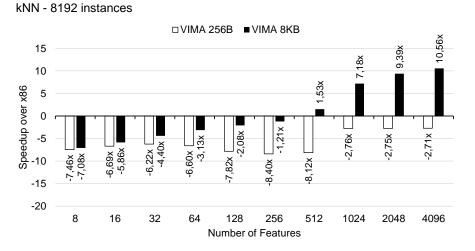

| 5.2  | VIMA's speedup over x86 for kNN with 8192 instances                               | 51 |

| 5.3  | VIMA's speedup over x86 for kNN with 16384 instances                              | 51 |

| 5.4  | VIMA's speedup over x86 for kNN with 32768 instances                              | 52 |

| 5.5  | VIMA's speedup over x86 for kNN with 65536 instances                              | 52 |

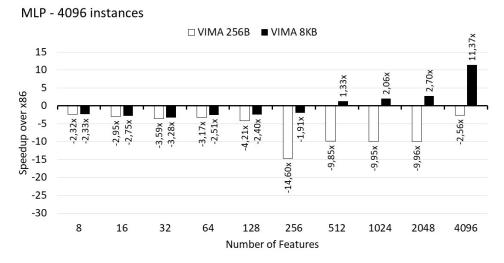

| 5.6  | VIMA's speedup over x86 for MLP with 4096 instances                               | 53 |

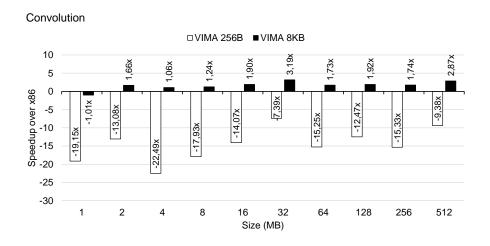

| 5.7  | VIMA's speedup over x86 for convolution                                           | 53 |

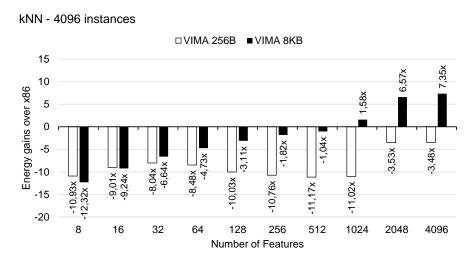

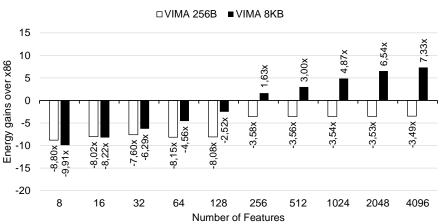

| 5.8  | VIMA's energy consumption over x86 for kNN with 4096 instances                    | 54 |

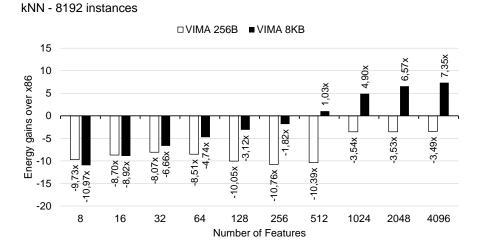

| 5.9  | VIMA's energy consumption over x86 for kNN with 8192 instances                    | 54 |

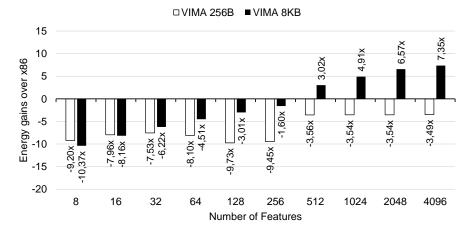

| 5.10 | VIMA's energy consumption over x86 for kNN with 16384 instances                   | 55 |

| 5.11 | VIMA's energy consumption over x86 for kNN with 32768 instances                   | 55 |

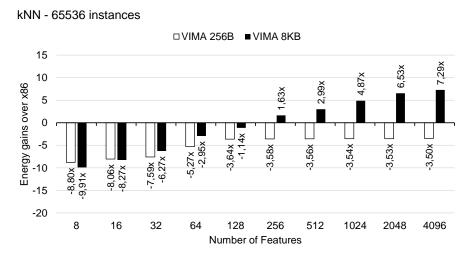

| 5.12 | VIMA's energy consumption over x86 for kNN with 65536 instances                   | 55 |

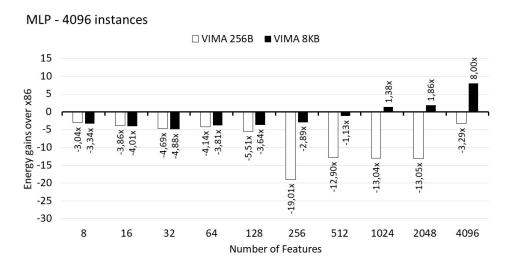

| 5.13 | VIMA's energy consumption over x86 for MLP with 4096 instances | 56 |

|------|----------------------------------------------------------------|----|

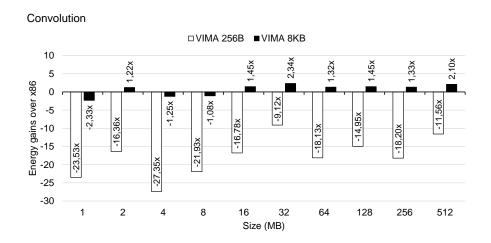

| 5.14 | VIMA's energy consumption over x86 for convolution             | 56 |

## LIST OF TABLES

| 2.1 | Bandwidths comparison                                              | 21 |

|-----|--------------------------------------------------------------------|----|

| 3.1 | Strings used in search base                                        | 27 |

| 3.2 | Inclusion/Exclusion criteria                                       | 28 |

| 3.3 | Summary of correlated papers characteristics                       | 29 |

| 4.1 | Intrinsics-VIMA data types                                         | 36 |

| 5.1 | Baseline and VIMA system configuration                             | 47 |

| 5.2 | kNN Memory Footprint approximation for VIMA 256B, 8KB and AVX512   | 49 |

| 5.3 | MLP Memory Footprint approximation for VIMA 256B, 8KB and AVX512   | 49 |

| 5.4 | Convolution Memory Footprint approx. for VIMA 256B, 8KB and AVX512 | 50 |

| A.1 | Table of Intrinsics-VIMA instructions                              | 70 |

| B.1 | Table of selected papers                                           | 78 |

## LIST OF ACRONYMS

| AI   | _ | Artificial Intelligence                 |

|------|---|-----------------------------------------|

| ALU  | _ | Arithmetic Logic Unit                   |

| API  | _ | Application Programming Interface       |

| APU  | _ | Accelerated Processing Unit             |

| ASIC | _ | Application Specific Integrated Circuit |

| AVX  | _ | Advanced Vector Extensions              |

| CNN  | _ | Convolutional Neural Network            |

| CPU  | _ | Central Processing Unit                 |

| DDR  | _ | Double Data Rate                        |

| DIMM | _ | Dual Inline Memory Module               |

| DMA  | _ | Direct Memory Access                    |

| DNN  | _ | Deep Neural Network                     |

| DRAM | _ | Dynamic Random Access Memory            |

| FP   | - | Floating-Point                          |

| FPGA | _ | Field-Programmable Gate Array           |

| FU   | _ | Functional Unit                         |

| GPU  | - | Graphics Processing Unit                |

| HBM  | _ | High Bandwidth Memory                   |

| HIVE | _ | HMC Instruction Vector Extensions       |

| HMC  | _ | Hybrid Memory Cube                      |

| HPC  | _ | High Processing Computing               |

| ISA  | _ | Instruction Set Architecture            |

| kNN  | _ | k-Nearest Neighbors                     |

|      |   |                                         |

| LLC    | _ | Last-Level Cache                                   |

|--------|---|----------------------------------------------------|

| LUT    | _ | Look-Up-Table                                      |

| MAPLE  | _ | MAssively Parallel Learning/Classification Engine  |

| MIMD   | _ | Multiple Instruction, Multiple Data                |

| MIPS   | _ | Microprocessor without Interlocked Pipeline Stages |

| ML     | _ | Machine Learning                                   |

| MLP    | _ | Multi Layer Perceptron                             |

| MMX    | _ | Multi-Media eXtensions                             |

| MRAM   | _ | Magnetoresistive Random-Access Memory              |

| NDP    | _ | Near-Data Processing                               |

| NIM    | _ | Neuron In-Memory                                   |

| NN     | _ | Neural Network                                     |

| NoC    | _ | Network-on-Chip                                    |

| 000    | _ | Out-of-Order                                       |

| OrCS   | _ | Ordinary Computer Simulator                        |

| PE     | _ | Processing Element                                 |

| PIM    | _ | Processing-In-Memory                               |

| ReLU   | _ | Rectified Linear Units                             |

| RISC   | _ | Reduced Instruction Set Computer                   |

| RRAM   | _ | Resistive Random-Access Memory                     |

| RVU    | _ | Reconfigurable Vector Unit                         |

| SIMD   | _ | Single Instruction Multiple Data                   |

| SiNUCA | _ | Simulator of Non-Uniform Cache Architectures       |

| SRAM   | _ | Static Random Access Memory                        |

| SSE    | _ | Streaming SIMD Extensions                          |

| TLB    | _ | Translation Look-aside Buffer                      |

TSV – Through-Silicon Via

VIMA – Vector-in-Memory Architecture

## CONTENTS

| 1     | INTRODUCTION                                         | 14 |

|-------|------------------------------------------------------|----|

| 2     | BACKGROUND                                           | 17 |

| 2.1   | MACHINE LEARNING                                     | 17 |

| 2.2   | COMPUTING PERFORMANCE                                | 18 |

| 2.3   | NEAR-DATA PROCESSING                                 | 19 |

| 2.4   | VECTOR-IN-MEMORY ARCHITECTURE                        | 21 |

| 2.5   | INTRINSICS LIBRARIES                                 | 24 |

| 2.6   | ORDINARY COMPUTING SIMULATOR                         | 24 |

| 3     | RELATED WORK USING SYSTEMATIC MAPPING                | 26 |

| 3.1   | SYSTEMATIC MAPPING METHODOLOGY                       | 26 |

| 3.2   | STATE-OF-THE-ART                                     | 30 |

| 3.2.1 | NDP Approaches with Full Cores                       | 31 |

| 3.2.2 | NDP Approaches with General-Purpose Cores            | 32 |

| 3.2.3 | NDP Approaches with Embedding Specific-Purpose Cores | 32 |

| 3.2.4 | DRAM and PIM Approaches                              | 33 |

| 3.2.5 | Conclusions on Related Work.                         | 34 |

| 4     | MACHINE LEARNING CODE PORTABILITY                    | 35 |

| 4.1   | INTRINSICS-VIMA                                      | 35 |

| 4.2   | OVERVIEW: MACHINE LEARNING KERNELS                   | 37 |

| 4.2.1 | Convolution Basics                                   | 37 |

| 4.2.2 | k-Nearest Neighbors (KNN) Basics.                    | 38 |

| 4.2.3 | Multi-Layer Perceptron (MLP) Basics                  | 38 |

| 4.3   | CODE PORTABILITY: VIMA                               | 41 |

| 4.3.1 | Convolution Migration                                | 41 |

| 4.3.2 | k-Nearest Neighbors (KNN) Migration                  | 42 |

| 4.3.3 | Multilayer Perceptron (MLP) Migration                | 44 |

| 5     | EXPERIMENTAL EVALUATION OF VIMA                      | 47 |

| 5.1   | METHODOLOGY AND SIMULATION SETUP                     | 47 |

| 5.2   | BEST CONDITIONS TO ACHIEVE HIGH PERFORMANCE          | 48 |

| 5.2.1 | k-Nearest Neighbors.                                 | 48 |

| 5.2.2 | Multilayer Perceptron                                | 49 |

| 5.2.3 | Convolution                                          | 49 |

| 5.3   | EXECUTION TIME RESULTS                               | 50 |

| 5.4   | ENERGY RESULTS                                       | 54 |

| 6 | FINAL CONSIDERATIONS                                       | 57  |

|---|------------------------------------------------------------|-----|

| 7 | CONCLUSION                                                 | 59  |

|   | REFERENCES                                                 | 60  |

|   | APPENDIX A – TABLE OF INTRINSICS-VIMA INSTRUCTIONS         | 69  |

|   | APPENDIX B – TABLE OF MAPPING STUDY                        | 77  |

|   | APPENDIX C – KNN ALGORITHM WITH AVX512                     | 81  |

|   | APPENDIX D – MLP HIDDEN LAYER ALGORITHM WITH AVX512 .      | 82  |

|   | APPENDIX E – MLP OUTPUT LAYER ALGORITHM WITH AVX512.       | 83  |

|   | APPENDIX F – CONVOLUTION ALGORITHM WITH AVX512             | 84  |

|   | APPENDIX G – KNN ALGORITHM WITH 8KB VIMA VECTOR            | 85  |

|   | APPENDIX H – KNN ALGORITHM WITH VIMA 8KB VECTOR            | 86  |

|   | APPENDIX I – MLP HIDDEN LAYER ALGORITHM WITH VIMA          |     |

|   | <b>8KB VECTOR</b>                                          | 87  |

|   | APPENDIX J – MLP HIDDEN LAYER ALGORITHM WITH VIMA          | ~ ~ |

|   |                                                            | 88  |

|   | APPENDIX K – CONVOLUTION ALGORITHM WITH VIMA 8KB<br>VECTOR | 60  |

|   |                                                            | 07  |

#### **1 INTRODUCTION**

Over the last two decades, digital data has increased significantly due to the increase of digital systems usage, which executes different kinds of transactions such as registration, creation, sharing, and downloading of information. For example, in 2011, the amount of created and replicated data surpassed 1.8 zettabytes, and predictions expect that this amount will grow  $9\times$  every five years. In this scenario, we can expect digital data volume to double every two years, reaching 40 trillion gigabytes at this year of 2020 (Gantz and Reinsel, 2011, 2012).

Those massive digital transactions carry lots of information about people's behavior in different aspects. All these data can be interesting for scientists and corporations to analyze to understand people's needs and develop personal products and services. Humans cannot analyze and understand this massive amount of data, firstly because of the volume and time required, secondly, due to its complexity. Thus, due to the increased processing capacity available in current computers, Machine Learning (ML) has gained popularity and became a useful tool to automate the analysis of massive amounts of data (Krizhevsky et al., 2012; Rakotomamonjy, 2003; Gardner and Dorling, 1998; Peterson, 2009; Dietterich, 2000).

ML was formalized in 1959 (Samuel, 1959) and focuses on systems that can learn and adapt to environmental changes without being explicitly programmed to it. Such algorithms rely on observations and sometimes learning from external examples to become capable of making their own decisions, identifying patterns, and making future decisions (Alpaydin, 2009).

Despite existing complex ML applications that are efficient in common architectures (Chen and Guestrin, 2016), some are memory and computationally intensive. Thus, experiments made in the last decades were mostly with small data sets, which changed with the current computer systems. Nevertheless, general-purpose computers and their ever-increasing performance still present severe bottlenecks in terms of the execution time of ML algorithms when dealing with real-world size problems (Boroumand et al., 2018). In this way, the most common implementations rely on accelerators and specific-hardware, such as Application Specific Integrated Circuit (ASIC), full Central Processing Units (CPUs), Field-Programmable Gate Arrays (FPGAs) (Nurvitadhi et al., 2016; Kara et al., 2017) and Graphics Processing Units (GPUs) (Gao et al., 2017; Ahn et al., 2016; Nair et al., 2015), which provide reasonable solutions due to their high computational capacity, allowing data parallelism and higher performance. Prominent designs based on simple vector units (e.g.,Functional Units (FUs)) (Alves et al., 2016; Santos et al., 2017; Oliveira et al., 2017a; Santos et al., 2018), also enable the highest energy efficiency while meeting the required constraints regarding the area and power (Lima et al., 2018).

Although all these alternatives can explore massive parallelism to execute ML algorithms, except for solutions implemented near memory, data movement between memory and the processor unit is still a bottleneck for data-intensive computations. Such a bottleneck is well known as memory-wall (Wulf and McKee, 1995). These previously mentioned devices rely on off-chip data transfer through interconnections (Ren, 2011; Sukhwani et al., 2012; Thoma et al., 2013). The memory-wall limitation is inherent to contemporary computer system designs, where the memory hierarchy can mitigate some of the performance drawbacks. However, in terms of energy and latency, it is not sufficient (Hashemi et al., 2016; Qureshi et al., 2007b,a).

Observing that data movement consumes as high as 60% of the total system energy (Boroumand et al., 2018), Near-Data Processing (NDP) and Processing-In-Memory (PIM) have emerged as promising solutions for the memory-wall problem, with the idea of integrating processor and memory in the same chip (Nowatzyk et al., 1996; Patterson et al., 1997b,a; Elliott et al., 1999b). These ideas emerged as a product in the last few years, such as Hybrid Memory Cube (HMC) and High Bandwidth Memory (HBM) (Hybrid Memory Cube Consortium, 2014; Kim and Kim, 2014). Such products take advantage of 3D integration technology to integrate processing logic and memory in the same chip, mitigating data movement and, consequently, reducing data latency and increasing processing and memory performance, achieving high data parallelism (Pugsley et al., 2014; Oliveira et al., 2017b).

Therefore, this dissertation proposes an alternative to achieve high-performance computing for ML applications, but still using a general-purpose architecture. The main idea is to present the benefits of migrating the kernel of three well-known ML algorithms (k-Nearest Neighbors (kNN), Multi Layer Perceptron (MLP), and Convolutional Neural Network (CNN)) to an NDP design capable of large-vector operations named Vector-in-Memory Architecture (VIMA). VIMA is inspired by HMC Instruction Vector Extensions (HIVE) (Alves et al., 2016) to provide a complete environment for NDP. It is a module attached to a 3D-stacked memory, composed of an instruction sequencer, vector FUs, and the most crucial component, a small cache memory. In this way, VIMA can reduce data movement between host processors and main memory, increasing overall efficiency and performance by executing vector operations and reusing data near memory.

These algorithms were chosen due to their usability to solve different types of ML problems and because of the code structure used to implement them, which is vastly used in computing and allows data reuse during execution. Besides, these algorithms were evaluated with different sizes of datasets to observe their behavioral changes in VIMA. These characteristics are relevant here since we expect a higher performance from VIMA considering bigger datasets.

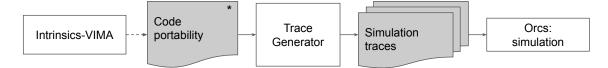

To allow this migration, we developed Intrinsics-VIMA, a vector-designed C/C++ library extension (Cordeiro et al., 2017). Intrinsics-VIMA facilitates the writing of codes for VIMA and similar NDP architectures, enabling the simulation and evaluation of new algorithms with reduced programming effort. As it is an x86-based library, the developer can use it like any other C/C++ library, enabling compilation, execution, and debugging.

The Intrinsics-VIMA library allows the generation of simulation traces to be consumed and evaluated by Ordinary Computer Simulator (OrCS), an in-house trace-driven simulator adopted to generate architectural results related to each application. The simulation traces are generated by an instrumentation tool, which analyzes the x86 binary code of the applications and introduces assembly VIMA instructions to the trace, when necessary. The simulator correctly interprets these assembly VIMA instructions.

Overall, in this dissertation, we present the evaluation of VIMA, a new NDP architecture, which mainly allows vector execution and data reuse, with vastly used algorithms of ML field. However, we do not intend to propose or evaluate ML algorithms, but on the architecture performance. Moreover, we also provide insights on how to migrate these algorithms to VIMA, considering the usage of large vector units and adjusting the algorithm to make better use of these units.

Our experimental results comparing the x86-only approach to the NDP migration show substantial improvements on execution time up to  $10\times$  for kNN,  $11\times$  for MLP, and  $3\times$  for convolution. Additionally, VIMA reduces energy consumption by up to  $7\times$  for kNN,  $8\times$  for MLP, and  $3\times$  for convolution.

In this dissertation, we present the following main contributions:

• We provide insights on how to migrate ML algorithms to a NDP architecture based on large vector units, showing benefits from NDP in this context.

• We extend and use an NDP intrinsics library that supports validation of NDP architectures based on large vectors.

The remaining of this document is organized as follows: Chapter 2, explains basic concepts for a better understanding of the proposal, discussing ML, NDP, OrCS, and Intrinsics libraries; Chapter 3 explains the research methodology and presents related work; Chapter 4 presents the main proposal of this work and expectations about it; Chapter 5 exhibits the obtained results related to speedup and energy efficiency and, finally; Chapter 7 brings final thoughts and future work.

#### 2 BACKGROUND

Among the related issues, in this chapter we detail ML, computational limitations, NDP, VIMA, OrCS, Intrinsics libraries, and a trace generator using Pin.

#### 2.1 MACHINE LEARNING

ML emerged in 1959 as a subfield of Artificial Intelligence (AI) and is concerned with studying the learning capacity of the firsts digital computers, developed around 1945. Those machines were capable of solving simple operations, such as addition, subtraction, and multiplication. However, researchers wanted to find a way to make those machines also "intelligent", a system that could learn by itself, without any programmer intervention. In this way, they strove to combine different abilities in digital computers, such as psychology, mathematics, philosophy, linguistics, and statistics, to enable it to analyze data and make its conclusions.

The main idea of ML is to enable a computer with no specific algorithm for a specific task to make correct decisions about it. In this way, the programmer must only input data and its correspondent labels when requested to a computer to its learning. The computer shall trace patterns used to classify newer samples or make a regression by predicting specific values. These kinds of tasks represent supervised learning techniques. Other techniques classified as unsupervised learning (Géron, 2019) relies on techniques such as: data clustering, dimensionality reduction, anomaly detection, or association rule learning. Another appealing paradigm is reinforcement learning, which allows progressive learning and can be applied in different fields of study, such as game theory, multi-agent systems, and statistics.

The specialist must add labels on the training dataset for supervised learning. The idea is to have an input instance and the desired output value to train the algorithm accurately. One of the most known techniques is classification, where an algorithm must be trained with a dataset to create a mathematical model representing that learning. Thus, during the training, the algorithm must frequently update a set of learning parameters considering each input's relevant features and its given label. After finishing the training phase, there will hardly be ideal values for these parameters to make the model accurate, so we must consider that there will be optimal values that will allow this. Besides, we consider a model accurate if it classifies the vast majority of the instances in a training dataset correctly. For some algorithms, such as Neural Networks (NNs) and Deep Neural Networks (DNNs), a bias is used along with the learning parameters to adjust the output better, and usually, the training phase is executed more than once. Each iteration in this process in the training dataset is called an epoch. Overall, the main objective of the training step is to reduce classification errors in the training dataset.

There is no label in the training dataset for unsupervised learning since these algorithms can group data in clusters considering specific attributes with undetected patterns that can make them similar between themselves. Thus, dimensionality reduction can simplify data without losing relevant information by extracting each data point's most relevant features. Anomaly detection algorithms can identify frauds and anomalies in datasets by detecting statistical outliers in the dataset. Association rule learning can analyze data to associate patterns that occur together and can be indirectly related. Finally, the trained model can be predictive or descriptive (Alpaydin, 2009; Géron, 2019).

Unlike supervised learning, reinforcement learning is a technique of progressive learning that does not require input labels or even rely on mathematical models with approximation

functions. Instead, it focuses on finding optimal solutions considering a specific algorithm and an environment. In other words, an agent in an environment has a goal to reach and, to do, so it has to take action. Each action has a reward linked to it and leads the agent to a different state in this environment. Thus the objective is to maximize the cumulative sum of the rewards received during the taken actions to reach this goal. These actions are repeated successively since it has to be taken for each state until the agent reaches its goal (Mitchell, 1997).

After the training phase, the validation occurs. If the model is not accurate enough, the developer must train the model again, considering different characteristics, parameters, and a more representative training dataset (Russell and Norvig, 2016; Alpaydin, 2009). Depending on these algorithms' final purpose, the programmer shall provide other information or rules available to achieve accurate results. However, the programmer should not interfere with the algorithm's learning process when calculating the model parameters, as it is expected that the ML algorithm learn by itself.

Once the model is validated, the inference phase can start. Here, the ML algorithm will make decisions for each sample from a set of test samples, considering the mathematical parameters defined during the training phase. Both training and inference are computationintensive tasks. The training relies on latency since it depends on massive operations over a massive set of training instances during multiple epochs to define the model parameters. On the other hand, inference relies on high throughput to classify a stream of instances, representing real-time applications, making this phase more critical than training.

Thus, the training phase depends on robust architectures to achieve high-performance computing. While the inference can be executed even in embedded systems with limited hardware resources, such as FPGA and autonomous vehicles (McDanel et al., 2017; Qiu et al., 2016; Tian et al., 2018), which means that the model must be trained once to be used multiple times by multiple devices.

Nowadays, it is easier to employ ML in different tasks due to different frameworks available in high-level languages (Raschka, 2015) and a vast amount of accessible datasets used to train and test the models. Thus, in the last few years, we could see a flourishing of applications for different fields such as object identification tools, voice recognition, text context analysis. Researchers are using such algorithms in diverse areas as genetics (Libbrecht and Noble, 2015), cancer prognosis (Kourou et al., 2015), autonomous vehicles (Kuderer et al., 2015), and facial expressions (Bartlett et al., 2004). These are examples of tasks that have the potential to bring a great advance in science for society.

For the remain of this dissertation, we consider to work with three ML kernels: kNN, MLP, and CNN. We implemented naive versions of each algorithm, and we intend to show just the most significant computation part of each algorithm since the idea is to evaluate them in VIMA. For example, the kernel of CNN is the convolution part only, while the ML is a plain NN where we implemented the inference part only. Together, they are a simplified version of CNN, which results give us an estimate of the whole algorithm. Further explanations of these algorithms will be present in Chapter 4.

#### 2.2 COMPUTING PERFORMANCE

Although ML offers a series of exciting solutions, it is not always possible to make proper use of this tool in a general-purpose processor. When working with a massive amount of data, complex ML algorithms can be computationally consuming, resulting in low performance. This low performance is due to the Von Neumann bottleneck, in which CPU and Dynamic Random Access

Memory (DRAM) communication restricts the computation capacity, i.e., the speed to acquire data from DRAM is significantly slower than the data processing speed (Shen and Lipasti, 2013).

Over the years, architects proposed different approaches to mitigate this bottleneck. The firsts attempts to improve performance emerged around 1980 with the cache memory, which inserts one level of a smaller and faster memory between CPU and memory. In this way, the cache will store recently used data and fetch it to the CPU faster than the DRAM (Smith, 1982; Shen and Lipasti, 2013).

Around 1990, superscalar in-order and Out-of-Order (OoO) processors emerged with a deeper pipeline, enabling fetching and executing more than one instruction per cycle. In the execution step, instructions with no dependencies can be executed before its predecessors, improving performance aggressively. By the same time, Single Instruction Multiple Data (SIMD) instructions became famous in the '90s with the Multi-Media eXtensions (MMX) Intel instruction set, followed by Streaming SIMD Extensions (SSE) and Advanced Vector Extensions (AVX) (20 years later), enabling the execution of vector instructions. In other words, they were implementing a specific operation over a set of operands in a few cycles (Shen and Lipasti, 2013).

According to Moore's Law, every 18 months (and currently every 24 months), the number of transistors shall double, resulting in increased processing capacity (Moore, 1998; Moore et al., 1975). Initially, architects made these technological integration improvements to convert in performance gains directly. However, this is no longer true nowadays due to problems such as memory-wall (Wulf and McKee, 1995) and dark silicon (Esmaeilzadeh et al., 2011). In summary, the CPU has dramatically improved over the years, but memory improvements are happening at a much slower pace (Efnusheva et al., 2017).

Besides, despite the improvements in general computing performance, energy consumption is still a problem, as 60% of the energy spent during execution refers to the data movement between processor and memory (Boroumand et al., 2018). Thus, the energy problem will remain even when executing ML algorithms in accelerators and specific-purpose hardware to achieve higher performance, as these devices, such as FPGA and GPU, will still communicate with CPU and memory through the bus (Sukhwani et al., 2012; Thoma et al., 2013).

#### 2.3 NEAR-DATA PROCESSING

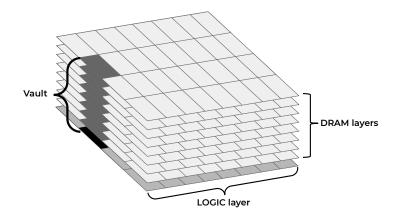

NDP dates back to the 1990s (Patterson et al., 1997b; Elliott et al., 1999a), when the industry was unable to integrate DRAM and logic cells on the same die. However, with the advent of 3D integration, NDP has reemerged as a viable solution. Architects came up with this new architecture concept to mitigate data movement between memory and processor. Thereby, processing occurs in the same chip as the memory, as illustrated in Figure 2.1. This type of architecture improves performance and energy consumption while presenting high parallelism, thus ensuring low average latency during high pressure in memory. Such architectures are ideal for streaming and parallel applications, graphics, High Processing Computing (HPC), and networking. Generally, any application with coalescent memory accesses can benefit from it.

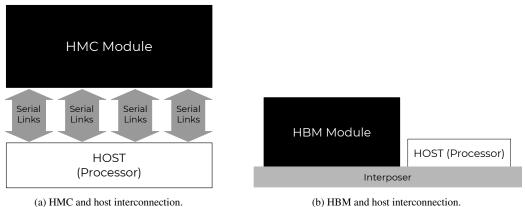

The most well-known 3D-stacked memory commercial examples are HMC (Hybrid Memory Cube Consortium, 2014) and HBM (Jun et al., 2017). Both architectures focus on the NDP concept, but some details differ between these. On the one hand, Micron released HMC in 2011 (Pawlowski, 2011b) with a completely new hardware and protocol specification. HMC used a 3D architecture to embed memory controller and processing logic near-data. It uses high-frequency serial links formed by full-duplex lanes, enabling data transmissions with low interference, to connect HMC to the processor (Thanh-Hoang et al., 2014). HMC is illustrated in Figure 2.2(a). Nevertheless, HMC requires a new protocol for memory control, which also

Figure 2.1: Block diagram of an 3D-stacked memory.

required changes on the processor side. On the other hand, HBM is JEDEC compliant since 2013 and has a well-known specification. Different from HMC, HBM is called a 2.5D architecture due to its integration system, which uses a silicon layer, called interposer, to attach both HBM memory and host CPU or GPU in the same die, as illustrated in Figure 2.2(b).

(a) HMC and host interconnection.

Figure 2.2: Block diagram of NDP architectures interconnection.

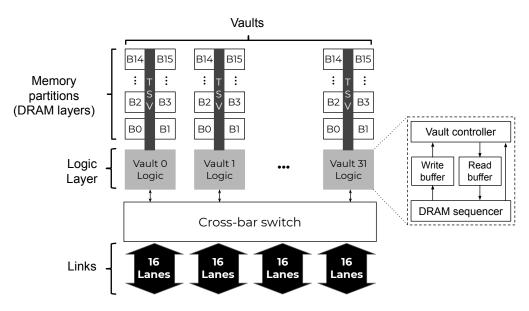

Overall, both architectures share several design characteristics. Both are compound by up to 8 stacked layers of DRAMs having a base that is a logic layer. Such a logic layer can integrate a processor to operate elements inside the memory. The 3D-stacked memory module is logically partitioned in up to 32 vaults, similar to the memory channel concept. Each vault is composed of up to 16 independent DRAM banks, distributed among DRAM layers, connected through Through-Silicon Vias (TSVs) (Olmen et al., 2008), as illustrated in Figure 2.3. NDP architectures can hide their data access internal latency due to their high bandwidth provided by internal parallelism (Hybrid Memory Cube Consortium, 2013; Jeddeloh and Keeth, 2012; Pawlowski, 2011a) achieved by 3D integration technology together with the 32 vaults.

Compared to Double Data Rate (DDR) memory technology, NDP devices require, on average, the same voltage level. However, 3D memories can achieve higher memory bandwidth, reaching up to 410 GB/s in the latest version (JESD235C) (Transcend, 2014; AMD, 2015), as defined in Table 2.1. It is also possible to observe that 3D-stacked memories have higher energy efficiency than DDR (Hrusca, 2015) due to its smaller row buffers and modified open row policy.

Finally, NDP can mitigate the memory-wall problem in contrast to CPU, GPU, and FPGA, which all require time and energy inefficient off-die (or off-chip) data transfers, by eliminating data movements from the memory hierarchy.

Figure 2.3: HMC block diagram with 32 vaults with 16 banks each one. Adopted from (Hybrid Memory Cube Consortium, 2013).

| Memory    | Bandwidth | Voltage | Speed (data<br>rate/pin) | Energy<br>efficiency | Jedec<br>standard |

|-----------|-----------|---------|--------------------------|----------------------|-------------------|

| DDR       | 3.2 GB/s  | 2.6 V   | 0.4 GT/s                 | 257.13 pJ/b          | yes               |

| DDR2      | 6.4 GB/s  | 1.8 V   | 0.8 GT/s                 | 121.44 pJ/b          | yes               |

| DDR3      | 14.9 GB/s | 1.5 V   | 1.8 GT/s                 | 64.70 pJ/b           | yes               |

| DDR4      | 25.6 GB/s | 1.2 V   | 3.2 GT/s                 | 38.67 pJ/b           | yes               |

| DDR5      | 41.6 GB/s | 1.1 V   | 5.2 GT/s                 | N.A.                 | yes               |

| HMC       | 320 GB/s  | 1.2 V   | 2.5 GT/s                 | 10.82 pJ/b           | no                |

| HBM1      | 128 GB/s  | 1.3 V   | 1.2 GT/s                 | N.A.                 | yes               |

| HBM2      | 256 GB/s  | 1.3 V   | 2.0 GT/s                 | N.A.                 | yes               |

| HBM2 2018 | 310 GB/s  | 1.2 V   | 2.4 GT/s                 | N.A.                 | yes               |

| HBM2e     | 410 GB/s  | 1.2 V   | 3.2 GT/s                 | N.A.                 | yes               |

Table 2.1: Bandwidths comparison.

#### 2.4 VECTOR-IN-MEMORY ARCHITECTURE

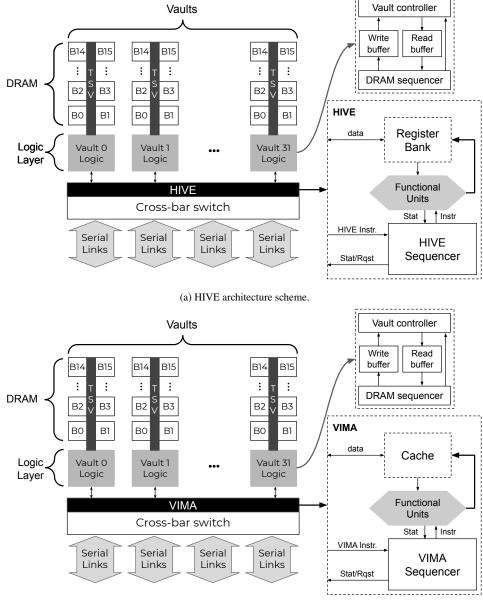

The main idea of this work is to evaluate ML algorithms in an NDP general-purpose processing that enables vector operation and does not require a full processor integration near data. In this context, HIVE enables the execution of large vector instructions that obtain data in parallel from the independent memory vaults inside a 3D-memory. It also includes vector extensions to the processor's Instruction Set Architecture (ISA) to control the near-data vector units. This design does not require any complex instruction fetch or decode unit implementation inside the memory. HIVE (Alves et al., 2016) was adopted as a model to define VIMA, that we will use in this dissertation.

VIMA is similar to other NDP approaches, which obtain data from several independent memory vaults in parallel (Alves et al., 2016; Santos et al., 2017; Tomé et al., 2018). The main difference is that VIMA replaces HIVE's register bank with a data cache memory of a similar size (i.e., 64 KB), which maintains high performance while providing transparency and high flexibility for programmers, as depicted in Figure 2.4. VIMA explores the data access parallelism inherent

to NDP architecture, and its cache enables fast reuse of vectorized data within the memory. Both HIVE and VIMA proposals support ARM NEON Integer and Floating-Point (FP) instructions, operating over vectors of 8 KB of data, which fetch data over the 32 channels (vaults) in parallel.

(b) VIMA architecture scheme.

Figure 2.4: Architectural difference between HIVE and VIMA.

The main physical addition of VIMA compared to related work Alves et al. (2016); Santos et al. (2017) is a small cache memory that enables data-reuse of data vectors. One could perceive this as a minor change, but VIMA enables significant improvements due to its new operation rationale, such as improved data re-usage, easy-to-program interface, precise exceptions, extensible design, multi-threading, all discussed in the next sub-sections. At the same time, it maintains most of the performance improvements compared to any NDP strategy.

Similar to SSE, AVX, and NEON instruction sets, VIMA also needs an ISA extension, which must be used in the code by the programmer and is explained further, in section 2.5. VIMA instructions must be inserted in the application during compilation and pass through the processor

as a conventional memory instruction. However, they bypass the cache memory hierarchy, being sent directly to the 3D-stacked memory chip.

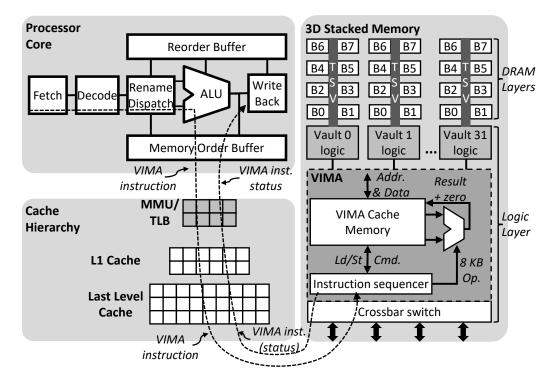

VIMA instructions operate over data vectors of 256 B and 8 KB. For instance, for a VIMA cache memory of 64 KB, it may store 32 vectors of 256 B, or 8 vectors of 8 KB. Beyond the cache memory, a set of vector FUs, and an instruction sequencer are added to VIMA, as depicted in Figure 2.5. Thus, as soon an instruction is sent to VIMA, it must wait in the sequencer until its required data is fetched from the 3D-stacked memory and become available in VIMA's cache memory. Then, the instruction executes in the vector FUs, and, as soon as it finishes, a signal is sent to the CPU, informing its execution status. If the execution is successful, the processor can commit the instruction. Otherwise, the pipeline must be flushed, and an exception is raised. VIMA executes instructions in-order to accomplish precise exceptions.

Figure 2.5: 3D-stacked memory module with VIMA architecture.

As the CPU dispatches the next VIMA instruction after committing the previous one, it has to deal with precise exceptions. Thus, it is possible to observe some negative impacts on VIMA. Firstly, an 8 KB vector enables the full parallelism of a 3D-stacked memory chip with 32 vaults and at least 8 banks per vault. However, 256 B vectors perform 74% worse than 8 KB in terms of execution time, on average. This performance decay happens because smaller vector sizes in VIMA, are unable to fully use the memory's internal parallelism. Secondly, precise-exceptions impose an in-order execution for VIMA instructions. Accordingly to our evaluations, these pipeline bubbles degrade between 2% and 4% the execution time.

VIMA maintains most of the high-performance of any NDP strategy while enabling significant improvements, such as improved data re-usage, easy-to-program interface, precise-exceptions, multi-threading, and extensible design. VIMA is flexible enough to allow changes in data vectors size, which may reduce or increase the parallelism inside the memory.

#### 2.5 INTRINSICS LIBRARIES

We developed Intrinsics-VIMA library to enable quick and easy development of programs using the NDP instructions. It is inspired by Intel Intrinsics (Lomont, 2011), a library available in C language with a set of routines. When a program calls a routine from this library, it embeds its internal assembly x86 code directly in the compiler to optimize the execution. The assembly code generated during the compilation of a C code with the same functionalities, but without calling Intel intrinsic functions, might not be the same (Coorporation, 2009). Thus, these routines allow low-level code optimization, including code vectorization, known as SIMD instructions. Nevertheless, the vendors create and distribute intrinsic libraries accordingly to the ISA extension available inside each processor. Intel intrinsics are typically used by expert programmers that want to obtain most of the processor's ISA performance.

VIMA is an ISA extension that is not present in real-world processors yet. Thus, our Intrinsics-VIMA is a library composed of routines that reproduce the behavior of VIMA, using x86 instructions. Intrinsics-VIMA was developed in C/C++, allowing programmers to write, compile, execute, and debug code even for a non-existing architecture, since it is possible to simulate it in the x86 environment, ensuring the code correctness. Whenever the code is reliable, we can use it to generate simulation traces. At this step, the trace generator converts the routines into VIMA instructions that our simulation environment can interpret and simulate. We provide more details regarding the trace generator in Section 2.6.

We already developed other Intrinsics libraries for different target architectures, such as Intrinsics-HMC (Cordeiro et al., 2017) and Intrinsics-MIPS. These Intrinsics libraries are easy to develop, test, and extend to different architectures. Besides, all the Intrinsics libraries are available in GitHub <sup>1</sup>. Intrinsics-VIMA was developed for this work and will be fully detailed in Chapter 4.

#### 2.6 ORDINARY COMPUTING SIMULATOR

During the evaluation of new processor architectures, simulation represents a viable and affordable solution for designers. It happens because the system to be evaluated is too complex to be handled by analytic models, and highly expensive to be prototyped (Jain, 1990). Thus, most computer architects use simulation tools. In contrast to full-system simulation, trace-driven simulators do not require real execution of the application instructions. Such simulators only consider the behavioral details (algorithmic) and microarchitectural latencies for the given traced instructions. These simulators use execution traces of real applications formed by one or multiple files containing the flow of instructions observed during the program execution. These traces can be generated manually by researchers or automatically by binary instrumentation tools.

In this work, we used OrCS, a cycle-accurate, trace-driven simulator, based on the x86 architecture, able to execute the ISAs x86\_32, x86\_64, and now, VIMA. OrCS is a simplified version of Simulator of Non-Uniform Cache Architectures (SiNUCA) (Alves et al., 2015; Alves, 2014). OrCS has a Trace Generator that automatically generates simulation traces from instrumented binaries.

To generate traces properly, we built the Trace Generator using Pin from Intel, a binary instrumentation and analysis tool. Pin allows the development of Pintools, which are programs developed, making use of Pin routines to define which code sections will be analyzed and which kind of analysis or operation must be executed in these sections. These Pintools are then executed with the binary file and perform the analysis during the execution using a just-in-time compiler.

https://github.com/AlineS/intrinsics

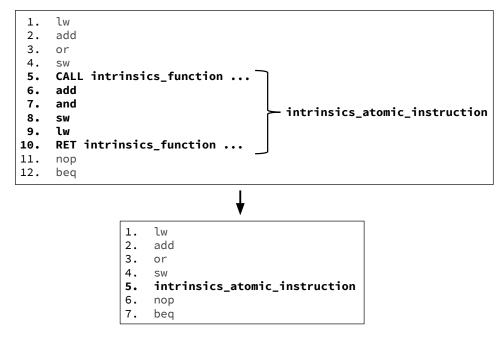

Inside the Trace Generator, our Pin-tool identifies every Intrinsics-VIMA function call in the binary file. It replaces all x86 assembly code generated during compilation by assembly code correspondent to VIMA. These replacements are written in the output simulation traces, as illustrated in Figure 2.6. Despite the changes inserted in the simulation traces, the behavior and main features defined during the x86 compilation, such as jump addresses and register usage, remain the same.

Figure 2.6: Example of x86 assembly replacement. This simplified example shows that the number of instructions is reduced in simulation traces, since blocks of x86 assembly code are replaced for single synthetic VIMA instructions.

Equal to SiNUCA traces, our simulation traces are divided into three types: static, dynamic, and memory. For further details on such traces, please refer to the SiNUCA paper (Alves et al., 2015; Alves, 2014).

When developing non-existing ISA, researchers usually write their simulation traces by hand. However, this is a painstaking and error-prone task, given the complexity from assembly development to correctly placing registers' dependency. Fortunately, OrCS enables users to automatically generate these traces for both existing and non-existing ISAs, thanks to our NDP-intrinsics library.

#### **3 RELATED WORK USING SYSTEMATIC MAPPING**

As soon as we defined the topic to be explored and developed in this dissertation, it was necessary to understand the current advances related to architecture and ML areas of research. Being aware of the most remarkable works and studies related to these ideas is also necessary to better understand the field and avoid mistakes such as improper tools, methods, or misconceptions cleared by past studies. Petersen et al. (2015) proposed a technique to create a reliable base for any research work called Systematic Mapping. This technique proposes a way to overview a research area by searching what topics are covered and where this literature has been published. These criteria can bring updates about recent and compelling research topics in areas of interest.

In this chapter, we used the Systematic Mapping methodology to find and understand the state-of-the-art about NDP architectures for ML applications.

#### 3.1 SYSTEMATIC MAPPING METHODOLOGY

Following the Systematic Mapping approach (Petersen et al., 2015), we defined some research questions based on the requirements in porting ML applications to NDP architectures:

- RQ1: What were the main objectives in evaluate ML applications in NDP or PIM architectures?

- RQ2: What kind of hardware was used?

- RQ3: Which components were used to build it?

- RQ4: What were the methods, tools, and mechanisms used to prototype and evaluate?

- RQ5: Which ML applications were chosen?

- RQ6: Which programming languages were used?

- RQ7: Do the researchers presented performance results?

- RQ8: In what institutions were the works developed?

It is possible to delimit this work with those questions. Firstly, by distinguishing processing elements, FUs, and its building blocks. Secondly, by distinguishing the tools used in porting and simulating these work, the programming languages used, and the results obtained. We also found it essential to know where these research works were developed to identify the leading research groups working in this area.

Thereby, we searched papers focusing on ML applications in NDP and PIM architectures in the IEEE Xplore, ACM Digital Library, and Springer Link bases, which provide advanced tools for a more accurate filter of papers. So, a boolean search was used on these bases, filtering by the computer science field.

Thus, we combined the strings "Processing-in-memory", "Processing-in-memory architecture", "In-memory processing", "In-memory architecture", "Near-data processing", "Processing-near-memory", "Data-centric computing", "Near-data computation", "In-memory computing", "Machine learning", "Deep Learning", and "Neural Network" to perform the searches and are presented in Table 3.1.

| Table 3.1: \$ | Strings | used in | search | base. |

|---------------|---------|---------|--------|-------|

|---------------|---------|---------|--------|-------|

| Search   | Date       | Search string                               |  |  |  |  |

|----------|------------|---------------------------------------------|--|--|--|--|

| base     |            |                                             |  |  |  |  |

| IEEE     |            | (("Processing-in-Memory" OR "In-Memory      |  |  |  |  |

| Xplore   | 18/07/2019 | Processing" OR "Processing-in-Memory        |  |  |  |  |

|          |            | architecture" OR "In-Memory architecture"   |  |  |  |  |

|          |            | OR "Near-data Processing" OR "data- centric |  |  |  |  |

|          |            | computing" OR "processing-near-memory" OR   |  |  |  |  |

|          |            | "in-memory computing") AND ("Machine        |  |  |  |  |

|          |            | Learning" OR "Artificial Intelligence" OR   |  |  |  |  |

|          |            | "Deep Learning" OR "Neural Network"))       |  |  |  |  |

| ACM      |            | (("Processing-in-Memory" OR "In-Memory      |  |  |  |  |

| Digital  | 18/07/2019 | Processing" OR "Processing-in-Memory        |  |  |  |  |

| Library  |            | architecture" OR "In-Memory architecture    |  |  |  |  |

|          |            | OR "Near-data Processing" OR "data-centric  |  |  |  |  |

|          |            | computing" OR "processing-near-memory" OR   |  |  |  |  |

|          |            | "Near-Data Computation" OR "in-memory       |  |  |  |  |

|          |            | computing") AND ("Machine Learning" OR      |  |  |  |  |

|          |            | "Artificial Intelligence" OR "Deep          |  |  |  |  |

|          |            | Learning" OR "Neural Network"))             |  |  |  |  |

| Springer |            | (("Processing-in-Memory" OR "In-Memory      |  |  |  |  |

| Link     | 18/07/2019 | Processing" OR "Processing-in-Memory        |  |  |  |  |

|          |            | architecture" OR "In-Memory architecture"   |  |  |  |  |

|          |            | OR "Near-data Processing" OR "data- centric |  |  |  |  |

|          |            | computing") AND ("Machine Learning" OR      |  |  |  |  |

|          |            | "Artificial Intelligence" OR "Deep          |  |  |  |  |

|          |            | Learning" OR "Neural Network"))             |  |  |  |  |

#### **Inclusion criteria:**

• Researches focusing on executing ML applications in PIM and NDP architectures or accelerators.

- Researches present performance results.

- Researches using only digital circuits.

### **Exclusion criteria:**

• Researches about ML applications without focusing on architectural aspects.

• Researches about PIM and NDP without focusing on ML applications.

• Researches using analog circuits, such as memristor, Resistive Random-Access Memory (RRAM), Magnetoresistive Random Access Memory (MRAM), Static Random-Access Memory (SRAM), and neuromorphic architectures.

- Surveys only analyzing the evolution of ML or memory and processor.

- Papers are not written in the English language.

• Incremental researches: publications that keep most content of each other just changing or adding some details.

These searches returned 437 papers considering the three search bases above where: 148 were from the IEEE Xplore base, 64 from ACM Digital Library, and 225 from Springer Link, in articles and conference papers. Authors of 57% of these papers were established in the USA or China, and 81% of the papers are 5-year or less. However, we also considered older papers to find relevant information about PIM and NDP concepts and optimized algorithm implementations.

In the first search, we found a large number of papers, so it was necessary to refine it. Thus, we created some inclusion/exclusion criteria, which are presented in Table 3.2. After this step, we selected 27 papers plus one new find from the Google Scholar indexing site. The selected papers are presented in Appendix B.1. Moreover, 25 papers have similar proposes compared to this work, but were excluded according to Table 3.2 by its non-volatile memory and analog circuits employee, such as RRAM, MRAM, and neuromorphic architectures (Chi et al., 2016; Long et al., 2018; Angizi et al., 2018; Cheng et al., 2017; Pan et al., 2018b; Bojnordi and Ipek, 2016; Li et al., 2018; Shafiee et al., 2016; Ji et al., 2016; Agrawal et al., 2018; Lue et al., 2018; Fan and Angizi, 2017; Srivastava et al., 2018; Gupta et al., 2018; Yu et al., 2019; Chen et al., 2018; Imani et al., 2019b,a; Jiang et al., 2019; Imani et al., 2018) since these works use different processing approaches and technologies, such as current and voltage variations to process analog signals to calculate a NN.

Between those 27 papers, we selected only one from the 19% that referred to the older papers. Generally, these papers' main goal is to achieve better performance and less energy consumption by executing ML applications. From these works, 59% of the papers explicitly consider NDP or PIM concept; 82% presents parallelism and code optimization; 56% developed frameworks to implement ML codes; 6% consider different architectures such as Very Long Instruction Word and Automata Processor. Initially, we did not consider specific-purpose hardware research since this work employs a general-purpose processor. However, the amount of work using specific-purpose processors was considerable, and some of these papers are relevant to this work. Therefore, after following the guidelines of systematic mapping, we considered 18 papers as related work: Cadambi et al. (2010), Thottethodi et al. (2018), Li et al. (2017), Ahn et al. (2016), Xu et al. (2015), Gao et al. (2015), Oliveira et al. (2017a), Azarkhish et al. (2019), Gao et al. (2017b), Schuiki et al. (2018), Liu et al. (2018), Min et al. (2019),

| Paper                     | General /        | Vector / | Near-memory | # Full |

|---------------------------|------------------|----------|-------------|--------|

| _                         | Specific Purpose | Scalar   | / In-memory | cores  |

| Cadambi et al. (2010)     | General          | Vector   | Near-memory | N      |

| Thottethodi et al. (2018) | General          | Vector   | Near-memory | N      |

| Li et al. (2017)          | General          | Vector   | In-memory   | 1      |

| Ahn et al. (2016)         | General          | Scalar   | Near-memory | N      |

| Xu et al. (2015)          | General          | Scalar   | Near-memory | N      |

| Gao et al. (2015)         | General          | Scalar   | Near-memory | N      |

| Oliveira et al. (2017a)   | General          | Vector   | In-memory   | 1      |

| de Lima et al. (2019)     | General          | Vector   | Near-memory | N      |

| Azarkhish et al. (2018)   | Specific         | Vector   | Near-memory | N      |

| Gao et al. (2017)         | Specific         | Vector   | Near-memory | N      |

| Gao et al. (2018)         | Specific         | Scalar   | In-memory   | 1      |

| Schuiki et al. (2018)     | Specific         | Scalar   | Near-memory | N      |

| Liu et al. (2018)         | Specific         | Scalar   | Near-memory | N      |

| Min et al. (2019)         | Specific         | Scalar   | Near-memory | 1      |

| Deng et al. (2018)        | Specific         | Scalar   | In-memory   | 1      |

| Ganguly et al. (2018)     | Specific         | Scalar   | Near-Memory | 1      |

| Sim et al. (2018)         | Specific         | Scalar   | In-memory   | 1      |

| Deng et al. (2019)        | Specific         | Vector   | In-memory   | 1      |

| VIMA                      | General          | Vector   | In-memory   | 1      |

Table 3.3: Summary of correlated papers characteristics.

Deng et al. (2018), Ganguly et al. (2018), Sim et al. (2018), de Lima et al. (2019), and Deng et al. (2019) and they were summarized in Table 3.3, which highlights four characteristics considered important by us considering migration of ML applications to a NDP architecture and will be explained below.

To understand how these previous work are related and to point the similarities and differences between this work and the previous ones, we selected some relevant characteristics relying on architecture to achieve high performance for ML algorithms, such as:

- (i) A general or specific-purpose architecture: Focus on a general-purpose architecture that can achieve high performance in ML applications without disregarding another kind of application.

- (ii) Vectorial or scalar operations: To consider vectorization of all Reduced Instruction Set Computer (RISC) operations used by ML applications, such as multiplication, addition, and boolean instructions.

- (iii) Using near-memory or in-memory approach: Focus on near-memory approach, in other words, making an effort to integrate a 3D-memory instead of trying to change memory cells to perform calculations.

- (iv) Integrating full cores or develop a simple circuit to perform operations: Full cores normally are more expensive computationally and in energy costs than simplified circuits or FUs to be attached to the 3D-memory. These characteristics can discriminate VIMA from others.

#### 3.2 STATE-OF-THE-ART

After reading the related work, we summarized information about the architecture configurations in Table 3.3. Liu et al. (2018), Cadambi et al. (2010), Thottethodi et al. (2018), Li et al. (2017), Sim et al. (2018), Deng et al. (2018), Azarkhish et al. (2018), Schuiki et al. (2018), Min et al. (2019), Ganguly et al. (2018), Xu et al. (2015), Gao et al. (2015), Deng et al. (2019), Sim et al. (2018), de Lima et al. (2019), and Sudarshan et al. (2019) rely on simulators to evaluate computational performance. Some of them also developed an Application Programming Interface (API) to provide a way for programmers to implement codes for their PIM and NDP architectures.

Liu et al. (2018), Cadambi et al. (2010), Ahn et al. (2016), Gao et al. (2018), and Sim et al. (2018) developed APIs to enable programmers to use their architectures in an easy way, with high-level code. For example, the API developed by Sim et al. (2018) allows the programmer to configure the system parameters and to allocate DRAM regions to execute specific functions. While Gao et al. (2015) and Gao et al. (2018) developed low-level APIs, in which the programmer's code remains the same, but the API initializes the NDP architecture, set the system environment configurations, executes synchronization, communication and memory mapping. Besides, the API developed by Ahn et al. (2016) implements different function calls to allow parallel programming considering their specific cores. Cadambi et al. (2010) also implemented a set of functions to be used in high-level code that can map Processing Elements (PEs) in memory and distribute data and functions between them. Liu et al. (2018) proposed an OpenCL extension to profile applications and dynamically map and schedule them into the architecture cores.

In contrast, VIMA is very simple as the programmer needs only to write a C/C++ code using Intrinsics-VIMA without worrying about the execution or memory allocation inside the architecture. Furthermore, our model is based on an x86 general-purpose architecture. The processor will fetch every instruction and send it to VIMA only when treating NDP instructions. The rest of the instructions are executed by the x86 processor using its FUs.

Gao et al. (2015) approach is similar to VIMA considering the API usage and simulation. Besides, it uses an API for the programmer to write the application without worrying about the execution inside the PIM architecture. Gao et al. (2018), Li et al. (2017), and Schuiki et al. (2018) use a library to compile the application and their scheduling code is done in low-level. Meanwhile, Gao et al. (2018), and de Lima et al. (2019) use a linked library to generate PIM application in x86 environment to be simulated in Gem5 simulator. Finally, Liu et al. (2018), and Ahn et al. (2016) also use Intel Pin to generate traces to simulate them. Most of these consider architectures with many cores inside the memory, so their API also enables the programmer to allocate the cores and distribute the functions to them, configure the accelerator, update page tables, and call their library functions. Besides, some consider full cores or simple cores for each vault, also allowing communication between the cores. VIMA's API and architecture are simpler than related work. Intrinsics-VIMA library shall be included and called in a conventional C/C++ implementation. While the VIMA architecture mainly requires a sequencer, a module of FUs, and cache memory to compute data.

We can divide related work into two groups, those based on 3D-stacked memories and those relying on Dual Inline Memory Module (DIMM) to accelerate ML applications. Thus, focusing on criteria described in Table 3.3, 12 related work used the 3D-stacked memories: Liu et al. (2018), Ahn et al. (2016), Thottethodi et al. (2018), Gao et al. (2015), Oliveira et al. (2017a), Hong et al. (2018), Azarkhish et al. (2018), Schuiki et al. (2018), Min et al. (2019), Gao et al. (2017), Xu et al. (2015), de Lima et al. (2019) while 6 modified conventional DRAM memories with integrated circuits: Deng et al. (2018), Gao et al. (2018), Li et al. (2017), Deng et al. (2019), Sudarshan et al. (2019), Sim et al. (2018). Among the related work using 3D-stacked memories

Azarkhish et al. (2018), Schuiki et al. (2018), Liu et al. (2018), Ahn et al. (2016), Gao et al. (2015), and Xu et al. (2015) employ full processing cores such as RISC-V, ARM, and Accelerated Processing Unit (APU), and Gao et al. (2017), Min et al. (2019), Thottethodi et al. (2018), and Cadambi et al. (2010) developed specific-purpose embed cores.

#### 3.2.1 NDP Approaches with Full Cores

Considering the related work that used 3D-stacked memories, we could observe that some integrated full processing cores or simple circuits in it. NeuroStream (Azarkhish et al., 2018) is a scalable PIM platform capable of running DNNs with large input sizes and arbitrary filter sizes, and based on NeuroStream, Schuiki et al. (2018) implements a near-memory acceleration engine that can be used to train state-of-the-art Deep Convolutional Neural Networks.

Both proposals implement a module composed of RISC-V cores with local cache, Direct Memory Access (DMA), and specific cores. The first work is called NeuroStream and the second one, Network Training Accelerator. These modules are connected to every 3D-stacked memory using the crossbar switch, and both proposals enable vectorizing a few instructions. Except for the use of several cores in these previous proposals, this dissertation is similar if considering that it attaches the VIMA vector module to the crossbar switch. However, considering that this VIMA module needs only a few components (a cache, FUs, and a sequencer), it is clear the simplicity of our proposal.

A different proposal by Liu et al. (2018) developed a heterogeneous PIM architecture to accelerate ML training models developed in conventional frameworks. This proposal implements in the HMC logic layer, a series of fixed-function logic and programmable cores. The fixed-function cores are composed of adders and multipliers, and the programmable functions are ARM-based cores, which can be loaded and offloaded with kernel functions through a communication scheme with the CPU host.

The Tesseract approach (Ahn et al., 2016) focuses on accelerating large-scale graph processing using an HMC module and integrating what is called a Tesseract core, a single-issue in-order ARM core. These cores can communicate with each other by a message-passing protocol because each core holds a local memory. Additionally, it uses two prefetch schemes to exploit the memories better. Although this work focuses only on graphs, it can be considered a related work, as graphs can represent NNs.

The NDP architecture proposal by Gao et al. (2015) develops the hardware and software of an NDP architecture for in-memory analytics frameworks, including MapReduce, graph processing, and DNNs. The authors employed a set of NDP ARM cores, Translation Lookaside Buffers (TLBs) and, virtual memory schemes. These cores can communicate through a vault router and share the physical address with the CPU host.

The fact of using a set of ARM and RISC-V cores or APUs in a 3D-staked memory logic layer makes those solutions too expensive computationally compared to VIMA. As mentioned above, our proposal relies on a PIM-enabled memory with a vector module attached to the crossbar switch composed of a cache, vector FUs, and a sequencer. Besides, VIMA does not rely on communication between vaults, sharing of physical address space, or complex virtual memory schemes to achieve high performance or parallelism. Instead, the host CPU communicates with the PIM-enabled memory during execution, identifying VIMA instructions, and sending it to the NDP device.

#### 3.2.2 NDP Approaches with General-Purpose Cores

Still considering the related work relying on 3D-stacked layers, some are general-purpose architectures that implement simple circuits, such as Neuron In-Memory (NIM) (Oliveira et al., 2017a), a PIM reconfigurable accelerator that can simulate biologically meaningful NNs of considerable size. NIM is a module composed of a register bank, complex processing units, and a sequencer. It is attached to the crossbar switch, with one NIM module for each vault. Although NIM enables executing vector instructions, its architecture has a design more complicated and expensive than VIMA due to requiring a module for each vault. In contrast, VIMA has only one module attached to the crossbar switch, enabling communication to all vaults.

Xu et al. (2015) focuses on the parallelization of CNN on a system with multiple PIM devices. The authors consider two APUs, which consists of CPU and GPU cores. One APU as a host connected to a 3D-memory and the other APU is integrated into the memory's logic layer. In this way, their module has additional overhead due to the bus communication or syscalls to use these devices, being less energy efficient than VIMA.

Finally, de Lima et al. (2019) considers a reconfigurable mechanism inside the PIM module to dynamically reduce or increase the number of active FUs as the application demands. To do so, they considered a Reconfigurable Vector Unit (RVU) module to each vault, which comprises a set of  $32 \times 8$ -byte multi-precision FUs, a Finite State Machine (FSM) to control the flow of RVU instructions and an  $8 \times 256$ -byte register file. The RVU modules can operate independently and execute vector instructions. Similar to our proposal, they use a specific compiler to generate simulation traces to the Gem5 simulator. However, their architecture has a design more complex than ours since it dynamically adjusts itself during execution. Besides, they still need a RVU for each vault to vectorize the execution.

#### 3.2.3 NDP Approaches with Embedding Specific-Purpose Cores

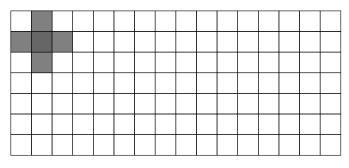

Among the related work relying on 3D-stacked layers, some implement simple and specific circuits, such as TETRIS (Gao et al., 2017) that is a proposal of a PIM NN accelerator, a software scheduling, and partitioning techniques. For each vault in a 3D-stacked memory, the authors propose hundreds of PEs connected through a dedicated network. Each PE is composed of an Arithmetic Logic Unit (ALU), an SRAM, and a register file. All PEs share a global buffer for communication.