## UNIVERSIDADE FEDERAL DO PARANÁ

#### TIAGO RODRIGO KEPE

## THE DESIGN AND IMPLEMENTATION OF QUERY EXECUTION IN MODERN PROCESSING-IN-MEMORY HARDWARE

Tese apresentada como requisito parcial à obtenção do grau de Doutor em Ciência da Computação no Programa de Pós-Graduação em Informática, Setor de Ciências Exatas, da Universidade Federal do Paraná.

Área de concentração: Ciência da Computação.

Orientador: Prof. Dr. Eduardo Cunha de Almeida.

Coorientador: Prof. Dr. Marco Antonio Zanata Alves.

CURITIBA 2019

# Catalogação na Fonte: Sistema de Bibliotecas, UFPR Biblioteca de Ciência e Tecnologia

٦

| K38d | <ul> <li>Kepe, Tiago Rodrigo</li> <li>The design and implementation of query execution in modern processing-<br/>in-memory hardware [recurso eletrônico] / Tiago Rodrigo Kepe. – Curitiba,<br/>2019.</li> </ul>                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Tese - Universidade Federal do Paraná, Setor de Ciências Exatas,<br>Programa de Pós-Graduação em Informática, 2019.                                                                                                                         |

|      | Orientador: Eduardo Cunha de Almeida. Coorientador: Marco Antonio Zanata Alves.                                                                                                                                                             |

|      | <ol> <li>Gerenciamento de memória (Computação).</li> <li>Big data.</li> <li>Banco de dados.</li> <li>Universidade Federal do Paraná.</li> <li>Almeida, Eduardo Cunha de .</li> <li>Alves, Marco Antonio Zanata.</li> <li>Título.</li> </ol> |

|      | CDD: 005.435                                                                                                                                                                                                                                |

|      |                                                                                                                                                                                                                                             |

Bibliotecária: Vanusa Maciel CRB- 9/1928

MINISTÉRIO DA EDUCAÇÃO SETOR DE CIENCIAS EXATAS UNIVERSIDADE FEDERAL DO PARANÁ PRÓ-REITORIA DE PESQUISA E PÓS-GRADUAÇÃO PROGRAMA DE PÓS-GRADUAÇÃO INFORMÁTICA -40001016034P5

#### TERMO DE APROVAÇÃO

Os membros da Banca Examinadora designada pelo Colegiado do Programa de Pós-Graduação em INFORMÁTICA da Universidade Federal do Paraná foram convocados para realizar a arguição da tese de Doutorado de **TIAGO RODRIGO KEPE** intitulada: **The Design and Implementation of Query Execution in Modern Processing-in-Memory Hardware**, sob orientação do Prof. Dr. EDUARDO CUNHA DE ALMEIDA, que após terem inquirido o aluno e realizada a avaliação do trabalho, são de parecer pela sua arguição vice forma de orientação.

A outorga do título de doutor está sujeita à homologação pelo colegiado, ao atendimento de todas as indicações e correções solicitadas pela banca e ao pleno atendimento das demandas regimentais do Programa de Pós-Graduação.

CURITIBA, 20 de Dezembro de 2019.

EDUARDO CUNHA DE ALMEIDA Presidente da Banca Examinadora

PHILIPPE OLIVIER ALEXANDRE NAVAUX Avaliador Externo (UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL)

> Daniel Ulimina Daniel alfonso goncalves de oliveira

Avaliador Interno (UNIVERSIDADE FEDERAL DO PARANÁ)

TONIO ZANATA ALVES MARCO AN

Coorientador (UNIVERSIDADE FEDERAL DO PARANÁ)

FABIO ANDRE MACHADO PORTO Avaliador Externo (LABORATÓRIO NACIONAL DE COMPUTAÇÃO CIÊNTÍFICA)

Rua Cel. Francisco H. dos Santos, 100 - Centro Politécnico da UFPR - CURITIBA - Paraná - Brasil CEP 81531-980 - Tel: (41) 3361-3101 - E-mail: ppginf@inf.ufpr.br

To my Lord who has gave me strength during all my years of study, especially during my doctoral.

"…

LORD has helped 'me' to now. " 1 Samuel 7:12

#### ACKNOWLEDGEMENTS

Firstly, I express my gratitude to Prof. Marco Zanata for insightful research conversations about computer architecture. Above all, my most sincere gratitude to Prof. Eduardo C. de Almeida for the guidance, patience, and continuous support over the last decade; my very thank you, I could not imagine a better advisor and mentor for my Ph.D., Master's and undergrad studies.

I would also like to thank all the professors and lab colleagues (LBD and HyPES) at UFPR, in special to Prof. Marcos Castilho and Daniel Weingaertner for the opportunity to join C3SL, one of the best places that I have worked and researched. I also remember the good talks and conference trips with Edson Ramiro, Simone Dominico, Eduardo Pena, and the remote ones in the Netherlands (CWI).

A special thanks to all my family. I would like to express my gratitude to my parents Rose and Julio for the unconditional support and wise advice, my brothers, and also my wife's family to the prayers and to believe in me.

Last but not least, I would like to express my gratitude to my beloved wife Bruna for standing beside me throughout my career and studies. You always believed in me from the early days of my baccalaureate, when I was still working at dawn, then came my master's degree and now doctorate; thank you very much, Bruna D. Kepe. Words are not enough to express how much I love you! Also, to my lovely son Paulo Vinícius, who was conceived at the end of my master's degree, thank you "Daddy's Didi" for being a beam of light in my life, you are one of the biggest inspirations to propel me beyond the edges.

#### RESUMO

Os sistemas modernos de processamento de consultas foram projetados com base em modelos de arquitetura centrados na computação. No entanto, o rápido crescimento de "*big data*" intensificou o problema de movimentação de dados ao realizar o processamento analítco de consultas: grandes quantidades de dados precisam passar pela memória até a CPU antes que qualquer computação ocorra. Portanto, esses sistemas são afetados pela movimentação de dados que degrada severamente o desempenho e exige muita energia durante a transferência de dados. Estudos recentes sobre a carga de trabalho do Google mostraram que cerca de 63% de energia é gasta em média na movimentação de dados. Para resolver esse problema oneroso, propomos explorar as arquiteturas Processamento-em-Memória (PIM) que invertem o processamento de dados tradicional, enviando a computação para a memória repercutindo no desempenho e na eficiência energética.

Nesta tese, demonstramos empiricamente que a movimentação de dados exerce grande influência nos sistemas de banco de dados atuais e identificamos os principais operadores de consulta que são afetados. Apresentamos um estudo experimental sobre o processamento de operadores de consulta SIMD (*Single Instruction Multiple Data*) em hardware PIM em comparação com processadores x86 modernos (ou seja, usando as instruções AVX512). Discutimos o tempo de execução e a diferença de eficiência energética entre essas arquiteturas. Este é o primeiro estudo experimental, na comunidade de bancos de dados, a discutir as compensações entre tempo de execução e consumo de energia entre PIM e x86 nos sistemas atuais de execução de consultas: materializado, vetorizado e *pipelined*. Como resultado, nós introduzimos um novo sistema híbrido de processamento de consultas PIM-x86 SIMD que incita novos desafios e oportunidades. Além disso, também discutimos os resultados de um escalonador de consultas híbridas ao intercalar a execução dos operadores de consultas SIMD entre o hardware de processamento PIM e x86. Em nossos resultados, o plano de consulta híbrido reduziu o tempo de execução em 45%. Também reduziu drasticamente o consumo de energia em mais de 2 vezes em comparação com os planos de consulta específicos para cada *hardware*.

Palavras-chave: Execução de Consulta 1. Processamento em Memória 2. Escalonador de Consulta Híbrido 3. Eficiência Energética 4.

#### ABSTRACT

Modern query execution systems have been designing upon compute-centric architecture models. However, the rapid growth of "big-data" intensified the problems of data movement, especially for processing analytic applications: Large amounts of data need to move through the memory up to the CPU before any computation takes place. Therefore, analytic database systems still pay for the data movement drawbacks that severely degrades performance and requires much energy during data transferring. Recent studies on Google's workload have shown that almost 63% of energy, on average, is spent in data movement. To tackle this costly problem, we propose to exploit the up-to-date Processing-in-Memory (PIM) architectures that invert the traditional data processing by pushing computation to memory with an impact on performance and energy efficiency.

In this thesis, we empirically demonstrate that data movement has an impact on today's database systems yet, and we identify the foremost query operators that undergo it. Therefore, we present an experimental study on processing query Single Instruction Multiple Data (SIMD) operators in PIM compared to the modern x86 processor (i.e., using AVX512 instructions). We discuss the execution time and energy efficiency gap between those architectures. However, this is the first experimental study, in the database community, to discuss the trade-offs of execution time and energy consumption between PIM and x86 in the current query execution models: materialized, vectorized, and pipelined. As a result, a new hybrid PIM-x86 SIMD query execution system is introduced, bringing new challenges and opportunities. Besides, we also discuss the results of a hybrid query scheduler when interleaving the execution of the SIMD query operators between PIM and x86 processing hardware. In our results, the hybrid query plan reduced the execution time by 45%. It also drastically reduced energy consumption by more than  $2 \times$  compared to hardware-specific query plans.

Keywords: Query Execution 1. Processing-in-Memory 2. Hybrid Query Scheduler 3. Energy Efficiency 4.

## LIST OF FIGURES

| 1.1  | The impact of data movement on MonetDB                                                                                                           | 19 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | A general architecture of a DBMS [28, 29]                                                                                                        | 23 |

| 2.2  | An SQL query and its corresponding query plan.                                                                                                   | 24 |

| 2.3  | The entity Person and an instance of its respective relational schema                                                                            | 25 |

| 2.4  | Row vs. Columnar layout. The arrows show the data access orientation, and the dashed blue lines depict the access to two columns on both layouts | 29 |

| 2.5  | OLTP query on the row-store layout.                                                                                                              | 30 |

| 2.6  | OLAP query on the <i>row-store</i> layout                                                                                                        | 31 |

| 2.7  | OLAP query on the <i>columnar</i> layout                                                                                                         | 32 |

| 2.8  | Volcano iterator model to the left and the query execution tree to the right (i.e. query plan)                                                   | 34 |

| 2.9  | Top-down diagram of a partial execution of the TPC-H Query 03 on MonetDB                                                                         | 37 |

| 2.10 | Top-down diagram of a simplified version of TPC-H Query 01 on MonetD-B/X100 [8].                                                                 | 40 |

| 2.11 | Example execution plan with pipeline breakers [49] and the respective compiled code                                                              | 43 |

| 3.1  | Memory hierarchy with the latency and size of all levels, and some corresponding related work.                                                   | 46 |

| 3.2  | Commom processor-per-head in database machines to processor-per-disk in Active Disks with disks in parallel [60]                                 | 47 |

| 3.3  | SSD general architecture                                                                                                                         | 49 |

| 4.1  | A 3D-stacked memory architecture comprised of memory and logic layers, and external links to receive memory requests and PIM instructions [18]   | 57 |

| 4.2  | State-of-the-art PIM architectures [99, 100, 23, 110]                                                                                            | 58 |

| 4.3  | A query datapath movement in a traditional von Neumann architecture plus a modern 3D-stacked memory with PIM and SIMD support [99]               | 60 |

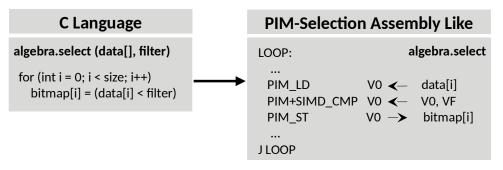

| 4.4  | The selection operator in PIM                                                                                                                    | 62 |

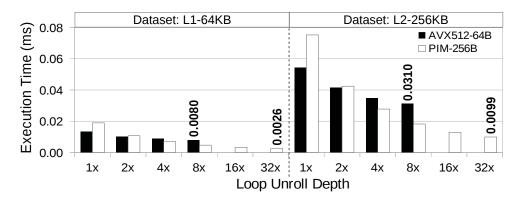

| 4.5  | Selection L1 and L2                                                                                                                              | 63 |

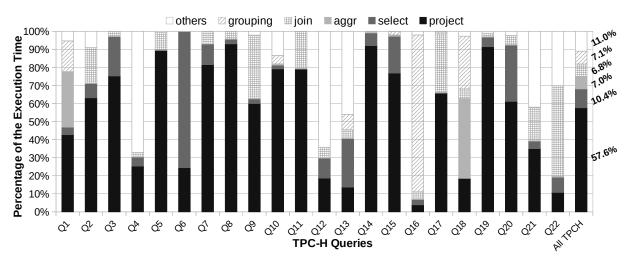

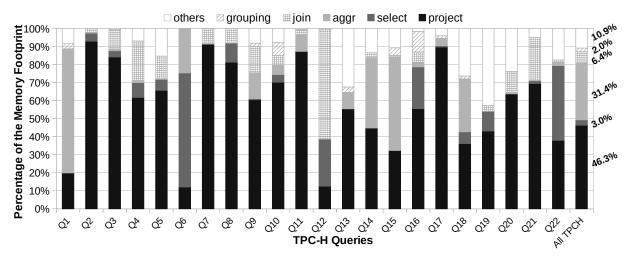

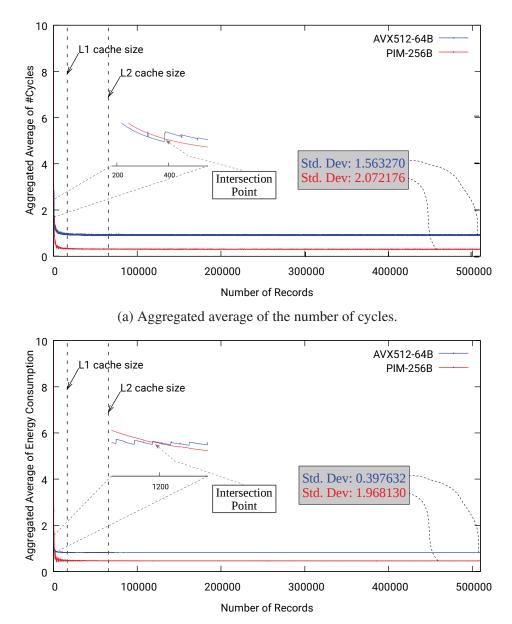

| 5.1 | Top time consuming database operators                                                                                                                                                                                                                                                               | 64 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2 | Top time consuming database operators                                                                                                                                                                                                                                                               | 65 |

| 5.3 | Selection Stability on SiNUCA.                                                                                                                                                                                                                                                                      | 69 |

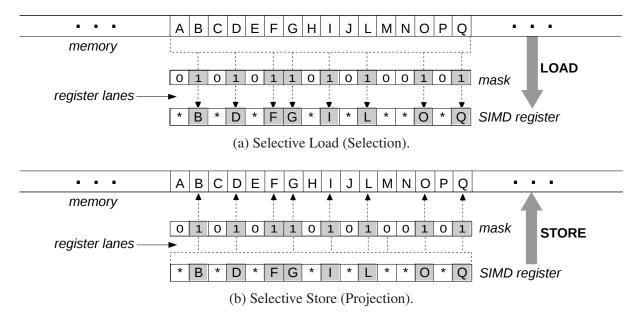

| 6.1 | SIMD memory instructions based on bitmask                                                                                                                                                                                                                                                           | 70 |

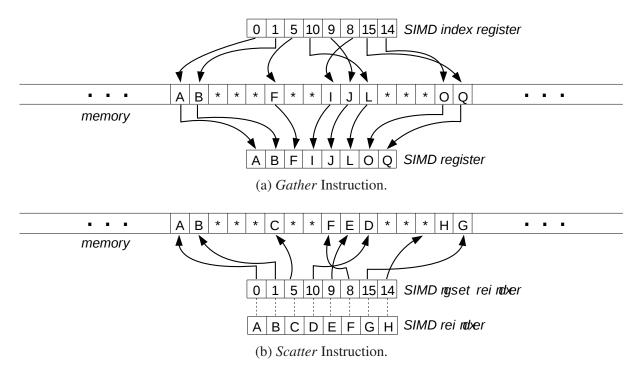

| 6.2 | SIMD memory instructions based on index register                                                                                                                                                                                                                                                    | 71 |

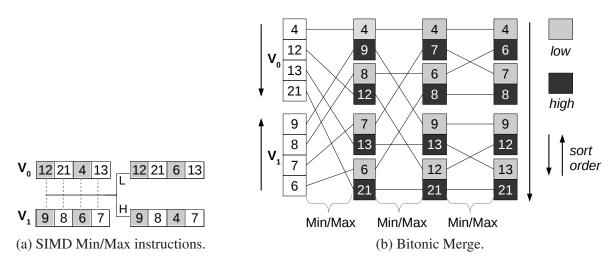

| 6.3 | <i>Min/Max</i> and <i>bitonic merge</i> examples                                                                                                                                                                                                                                                    | 73 |

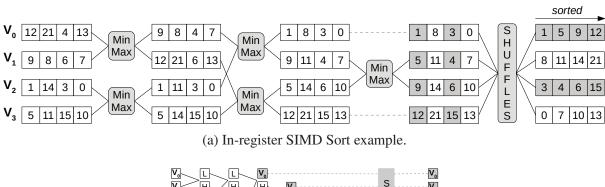

| 6.4 | SIMD Sort example and number of instructions, and the in-block-register Merge to combine sorted registers                                                                                                                                                                                           | 74 |

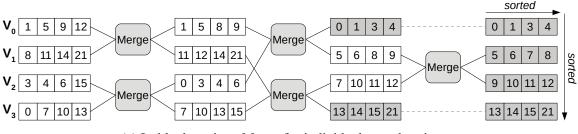

| 7.1 | Taxonomy of query operators                                                                                                                                                                                                                                                                         | 77 |

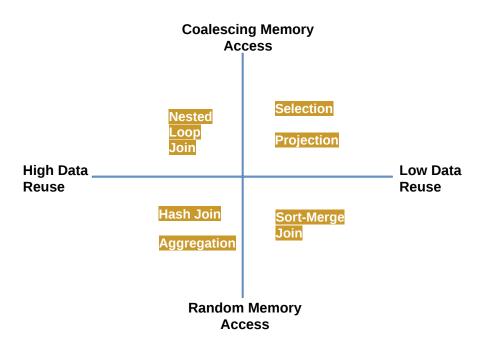

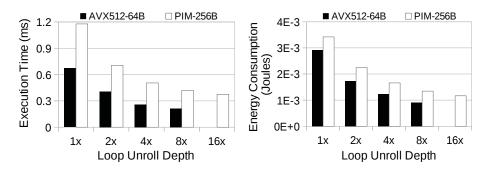

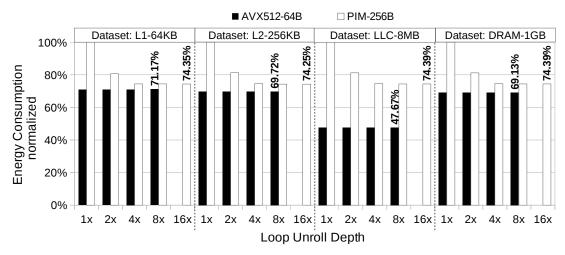

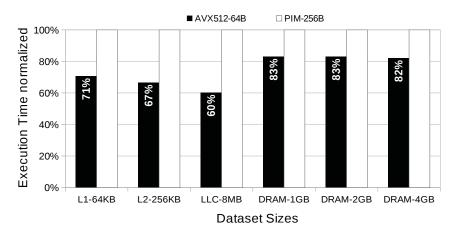

| 7.2 | Selection: Normalized execution time to the worst execution on the target architectures according to the size of datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, and DRAM-1GB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the AXV512 and up to $32 \times$ for PIM      | 78 |

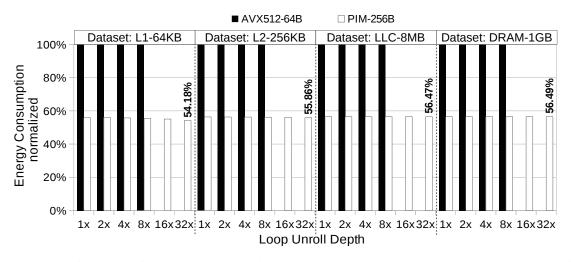

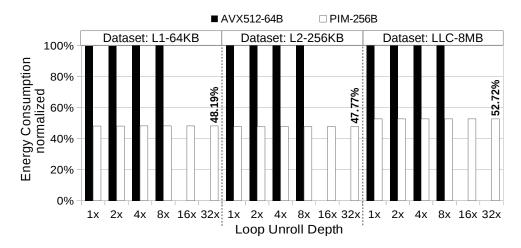

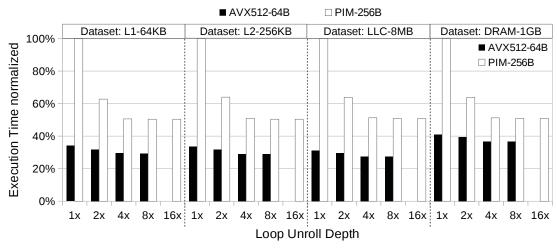

| 7.3 | Selection: Normalized energy consumption to the worst execution on the target architectures according to the size of datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, and DRAM-1GB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the AXV512 and up to $32 \times$ for PIM  | 79 |

| 7.4 | Projection: Normalized execution time to the worst execution on the target architectures according to the size of datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, and DRAM-1GB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the AXV512 and up to $32 \times$ for PIM     | 80 |

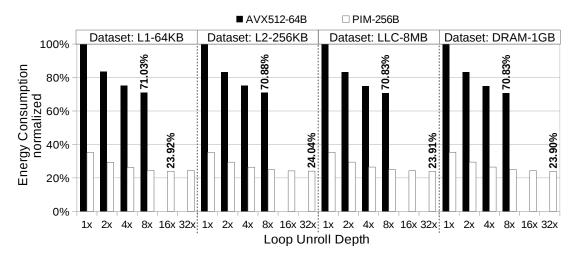

| 7.5 | Projection: Normalized energy consumption to the worst execution on the target architectures according to the size of datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, and DRAM-1GB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the AXV512 and up to $32 \times$ for PIM | 80 |

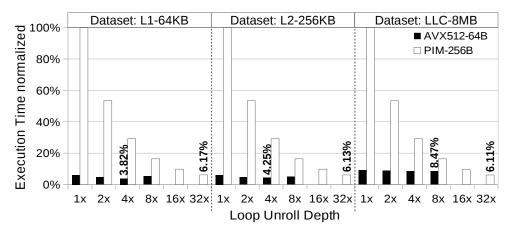

| 7.6 | NLJ: Normalized execution time to the worst execution on the target architectures according to the size of datasets (i.e., L1-64KB, L2-256KB, and LLC-8MB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the AXV512 and up to $32 \times$ for PIM                      | 81 |

| 7.7 | NLJ: Normalized energy consumption to the worst execution on the target ar-<br>chitectures according to the size of datasets (i.e., L1-64KB, L2-256KB, and<br>LLC-8MB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the<br>AXV512 and up to $32 \times$ for PIM       | 81 |

|     |                                                                                                                                                                                                                                                                                                     |    |

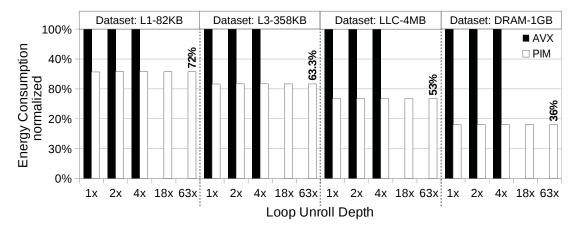

| 7.8  | Hash Join: Normalized energy consumption to the worst execution on the target architectures according to the size of datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, and DRAM-1GB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the AXV512 and up to $32 \times$ for PIM                     | 82 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.9  | Hash Join: Normalized energy consumption to the worst execution on the target architectures according to the size of datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, and DRAM-1GB). The x-axis varies the levels of parallel processing: up to $8 \times$ for the AXV512 and up to $32 \times$ for PIM                     | 83 |

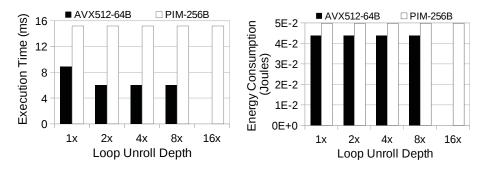

| 7.10 | Aggregation: the execution time of the TPC-H Query 01, varying the levels of parallel processing.                                                                                                                                                                                                                      | 83 |

| 7.11 | Aggregation: the execution time of the TPC-H Query 03, varying the levels of parallel processing.                                                                                                                                                                                                                      | 84 |

| 7.12 | Normalized execution time and energy consumption of the aggregation operator with the Zipf distribution. These performance metrics were normalized to the worst execution (i.e., PIM-256B $1\times$ ), varying the size of datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, and DRAM-1GB) and levels of parallel processing | 85 |

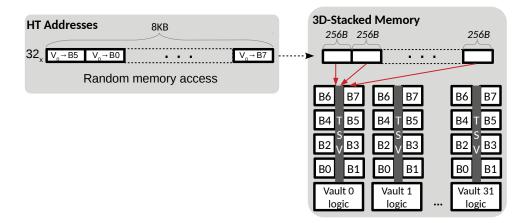

| 7.13 | Random memory access serialization to the vault $V_0$ within the PIM device, where $V_0 \rightarrow B_x$ is the access to the memory bank $B_x$ of the vault $V_0$                                                                                                                                                     | 86 |

| 7.14 | Sort-Merge Join: Normalized excecution time on the target architectures with loop unroll depth of 8x, varying the size of the datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, DRAM-1GB, DRAM-2GB, and DRAM-4GB)                                                                                                            | 86 |

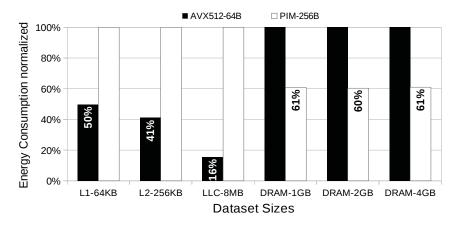

| 7.15 | Sort-Merge Join: Normalized energy consumption on the target architectures with loop unroll depth of 8x, varying the size of the datasets (i.e., L1-64KB, L2-256KB, LLC-8MB, DRAM-1GB, DRAM-2GB, and DRAM-4GB)                                                                                                         | 87 |

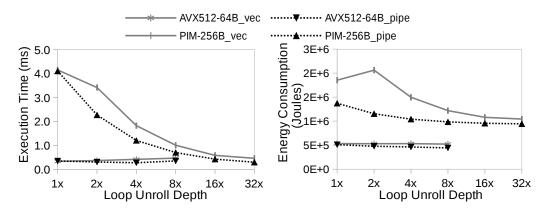

| 7.16 | Pipelined vs Vectorized execution on TPC-H Query 03 with a selection operator followed by building. The gray lines correspond to the vectorized execution model and black lines to the pipelined one                                                                                                                   | 88 |

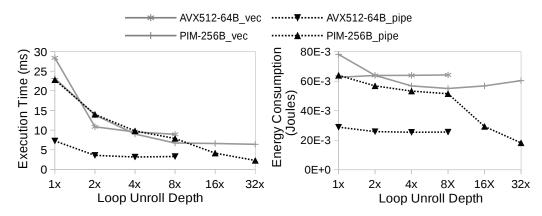

| 7.17 | Pipelined vs Vectorized execution on TPC-H Query 01 with a selection operator followed by aggregation. The gray lines correspond to the vectorized execution model and black lines to the pipelined one.                                                                                                               | 89 |

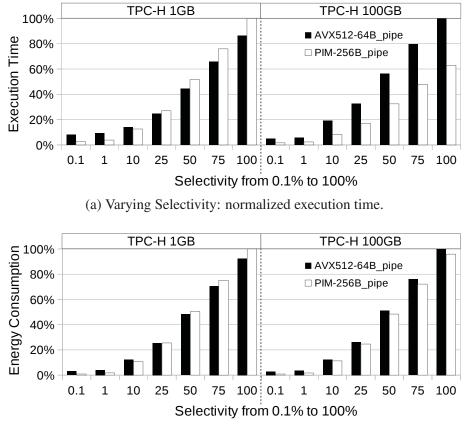

| 7.18 | Normalized execution time and energy consumption of the pipelined system according to the worst execution on datasets of 1GB and 100GB, varying the selectivity from 0.1% to 100%                                                                                                                                      | 90 |

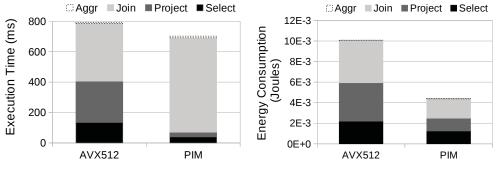

| 8.1  | TPC-H Query 03 execution breakdown in both target architectures.                                                                                                                                                                                                                                                       |    |

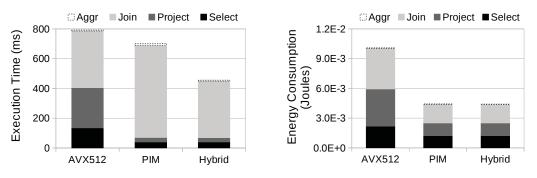

| 8.2 | Execution breakdown when applying our findings to process a hybrid query plan |    |

|-----|-------------------------------------------------------------------------------|----|

|     | for Query 3 in the target architectures                                       | 94 |

## LIST OF TABLES

| 2.1 | The join of the relations Person and Employee                                                    | 28 |

|-----|--------------------------------------------------------------------------------------------------|----|

| 3.1 | Related work summary of near-data processing for database operators                              | 55 |

| 5.1 | Workload and Dataset Summary                                                                     | 66 |

| 5.2 | Parameters of the target architectures taken into account to design the experi-<br>ments [110]   | 67 |

| 6.1 | Number of <i>min/max</i> instructions of the in-register SIMD sort computed by Equations 1 and 2 | 73 |

| 8.1 | Database Operators Summary.                                                                      | 93 |

## LIST OF ACRONYMS

| ALU  | Arithmetic Logic Unit             |

|------|-----------------------------------|

| AVX  | Advanced Vector Extension         |

| AD   | Active Disks                      |

| API  | Application Programming Interface |

| BAT  | Binary Association Table          |

| CPI  | Cycles Per Instruction            |

| CPU  | Central Processing Unit           |

| DBMS | Database Management System        |

| DDR  | Double Data Rate                  |

| DSS  | Decision Support System           |

| DMA  | Direct Memory Access              |

| DRAM | Dynamic Random-Access Memory      |

| ECC  | Correcting Code Memory            |

| GPU  | Graphics Processing Unit          |

| HBM  | High Bandwidth Memory             |

| HDD  | Hard Disk Driver                  |

| HIVE | HMC Instruction Vector Extensions |

| HPC  | High-Performance Computing        |

| HMC  | Hybrid Memory Cube                |

| HT   | Hash Table                        |

| IPB  | Instruction-Per-Byte              |

| IPC  | Instruction-Per-Cycle             |

| ISA  | Instruction Set Architecture      |

| JIT  | Just-In-Time                      |

| LLC  | Last Level Cache                  |

| LLVM | Low Level Virtual Machine         |

| MAL  | MonetDB Assembly Language         |

| MMU  | Memory Management Unit            |

| MR   | MapReduce                         |

| MSHR | Miss Status Handler Register      |

| NDP  | Near-Data Processing              |

| NLJ  | Nested Loop Join                  |

| nvm  | Non-Volatile Memory               |

| OoO  | Out-of-Order                      |

| OLAP | Online Analytical Processing      |

|      |                                   |

| OLTP   | Online Transaction Processing                |

|--------|----------------------------------------------|

| PCM    | Phase Change Memory                          |

| PIM    | Processing-in-Memory                         |

| RVU    | Reconfigurable Vector Unit                   |

| SIMD   | Single Instruction Multiple Data             |

| SiNUCA | Simulator of Non-Uniform Cache Architectures |

| SSD    | Solid-State Drive                            |

| SQL    | Structured Query Language                    |

| SSD    | Solid-State Drive                            |

| SSE    | Streaming SIMD Extensions                    |

| TSV    | Through-Silicon Via                          |

| VC     | Vault Controller                             |

## LIST OF SYMBOLS

| σ               | denotes a selection operator                                     |

|-----------------|------------------------------------------------------------------|

| $\pi,\Pi$       | denotes a projection operator                                    |

| Γ               | denotes a group by operator                                      |

| $\bowtie$       | denotes a join operator                                          |

| $\bowtie_{a=b}$ | denotes a hash table of a hash join, building from a and probing |

|                 | from <i>b</i>                                                    |

## CONTENTS

| 1     | INTRODUCTION                                    | 18 |

|-------|-------------------------------------------------|----|

| 1.1   | THE PROBLEM                                     | 19 |

| 1.2   | ΜΟΤΙVΑΤΙΟΝ                                      | 20 |

| 1.3   | HYPOTHESIS                                      | 20 |

| 1.4   | CONTRIBUTIONS                                   | 21 |

| 1.5   | ORGANIZATION                                    | 22 |

| 2     | DATABASE FOUNDATIONS                            | 23 |

| 2.1   | RELATIONAL MODEL                                | 24 |

| 2.2   | RELATIONAL ALGEBRA                              | 25 |

| 2.2.1 | Selection Operation                             | 26 |

| 2.2.2 | Projection Operation                            | 27 |

| 2.2.3 | Join Operation.                                 | 27 |

| 2.3   | STORAGE LAYOUT                                  | 28 |

| 2.3.1 | Row-Store Layout.                               | 29 |

| 2.3.2 | Colum-Store Layout                              | 30 |

| 2.4   | QUERY EXECUTION MODELS                          | 33 |

| 2.4.1 | The Volcano Query Execution Model               | 33 |

| 2.4.2 | The Materialization Query Execution Model.      | 34 |

| 2.4.3 | The Vectorized Query Execution Model            | 36 |

| 2.4.4 | The Pipelined Query Execution Model             | 41 |

| 2.5   | SUMMARY                                         | 43 |

| 3     | RELATED WORK                                    | 45 |

| 3.1   | NEAR-DATA PROCESSING IN MAGNETIC DISKS (HDD)    | 45 |

| 3.1.1 | Database Operators Processing in Magnetic Disks | 47 |

| 3.2   | FLASH DISKS (SSD)                               | 49 |

| 3.2.1 | Near-Data Processing In Flash Disks             | 50 |

| 3.3   | NON-VOLATILE MEMORY                             | 51 |

| 3.4   | MAIN MEMORY (DRAM)                                            | 52 |

|-------|---------------------------------------------------------------|----|

| 3.4.1 | Processing-In-Memory For Database Operators                   | 52 |

| 3.4.2 | Processing-In-Memory For Data Analytics.                      | 53 |

| 3.5   | SUMMARY                                                       | 54 |

| 4     | PROCESSING-IN-MEMORY ARCHITECTURE                             | 56 |

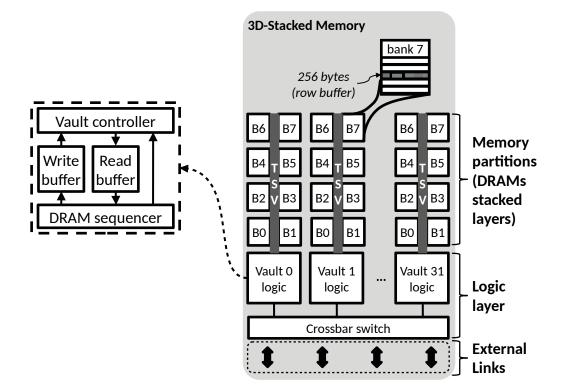

| 4.1   | 3D-STACKED MEMORY                                             | 56 |

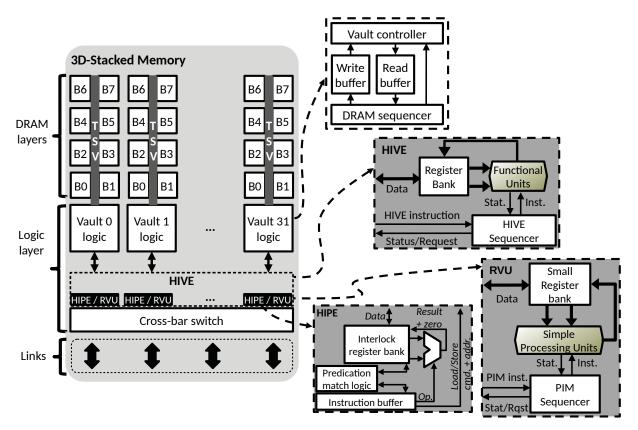

| 4.2   | 3D-STACKED MEMORY EXTENSIONS                                  | 58 |

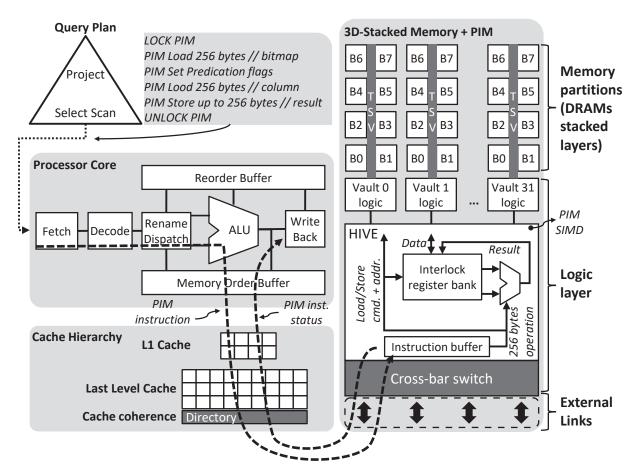

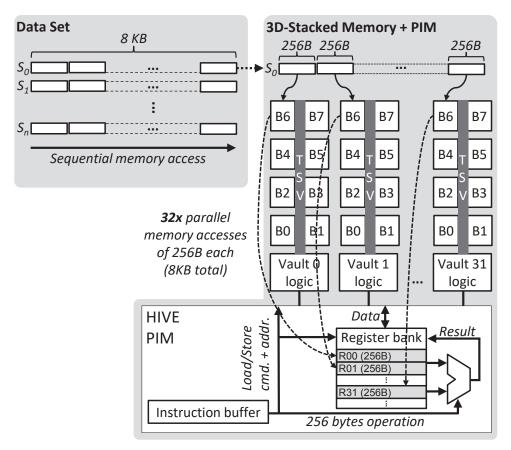

| 4.3   | HIVE: INSTRUCTION VECTOR EXTENSIONS                           | 59 |

| 4.4   | UNDERSTANDING THE PIM SELECTION                               | 60 |

| 4.5   | THE POTENTIAL PARALLELISM OF PIM-256B VS. X86 AVX512-64B      | 61 |

| 4.6   | SUMMARY                                                       | 63 |

| 5     | EXPERIMENT DESIGN                                             | 64 |

| 5.1   | CHOOSING THE GROUP OF OPERATORS                               | 64 |

| 5.2   | WORKLOAD'S DATA DISTRIBUTION                                  | 65 |

| 5.3   | SINUCA: A VALIDATED MICROARCHITECTURE SIMULATOR               | 66 |

| 5.3.1 | Validating the Simulation Stability of the Selection Operator | 68 |

| 5.4   | SUMMARY                                                       | 68 |

| 6     | IMPLEMENTATION DETAILS OF THE SIMD QUERY OPERATORS            | 70 |

| 6.1   | SIMD SELECTION AND PROJECTION OPERATORS                       | 70 |

| 6.2   | SIMD HASH JOIN AND AGGREGATION                                | 71 |

| 6.3   | SIMD SORT-MERGE ALGORITHM                                     | 72 |

| 6.4   | SUMMARY                                                       | 74 |

| 7     | RESULTS & ANALYSIS                                            | 76 |

| 7.1   | RELATED WORK                                                  | 76 |

| 7.2   | COALESCING MEMORY ACCESS AND LOW DATA REUSE                   | 77 |

| 7.2.1 | Selection Operator                                            | 78 |

| 7.2.2 | Projection Operator                                           | 79 |

| 7.3   | COALESCING MEMORY ACCESS AND HIGH DATA REUSE                  | 79 |

| 7.3.1 | Nested Loop Join                                              | 80 |

| 7.4   | RANDOM MEMORY ACCESS AND HIGH DATA REUSE                      | 81 |

| 7.4.1 | Hash Join                                                     | 82 |

| 7.4.2 | Aggregation Operator                       | 82 |

|-------|--------------------------------------------|----|

| 7.4.3 | Discussion.                                | 84 |

| 7.5   | RANDOM MEMORY ACCESS AND HIGH DATA REUSE   | 85 |

| 7.5.1 | Sort-Merge Join                            | 85 |

| 7.5.2 | Discussion.                                | 86 |

| 7.6   | PIPELINED VS. VECTORIZED QUERY EXECUTION   | 87 |

| 7.7   | THE EFFECT OF SELECTIVITY                  | 89 |

| 7.8   | SUMMARY                                    | 90 |

| 8     | HYBRID PIM-X86 SIMD QUERY EXECUTION SYSTEM | 92 |

| 8.1   | RELATED WORK & DISCUSSION                  | 92 |

| 8.2   | HYBRID PIM-X86 QUERY SCHEDULER             | 92 |

| 8.3   | CHALLENGES & OPPORTUNITIES                 | 94 |

| 9     | CONCLUSION & FUTURE WORK                   | 96 |

| 9.1   | FUTURE WORK                                | 98 |

| 9.2   | PUBLISHED PAPERS                           | 99 |

|       | REFERENCES                                 | 00 |

#### **1 INTRODUCTION**

Applications based on data analysis need to move large amounts of data between memory and processing units to look for patterns. Computers have relied on this traditional computing-centric processing since the introduction of the Von Neumann model, which detaches the processor core from the main memory. In this model, data movement severely affects performance and energy consumption. Recent studies show that data movement accounts for around 63%, on average, of the total energy consumption and imposes high latencies [1, 2].

The relational Database Management System (DBMS) is the essential component in modern computing environment to support the applications of data analysis. As defined by Silberschatz et al. [3]: The DBMS is a collection of interrelated data and a set of programs to access those data. In a DBMS, the query execution subsystem is the fundamental set of programs to support the applications of data analysis. This subsystem interacts with almost every component of a DBMS, like command compiler, concurrency control and recovery manager, but essentially it fetches data from the database and moves this data into memory buffers for processing. Modern DBMSs implement one of the following query execution models: materialized, vectorized and pipelined. However, these query execution models have been implemented only on computing-centric models [4]. The materialization query execution model generates lots of intermediate data that move along the memory hierarchy to process all the operators implemented by users in a query program [5, 6]. The vectorized query execution model tries to exploit the caching mechanism and the CPU processing with a high interpretation overhead of the query program [7, 8]. The pipelined query execution model uses the Just-In-Time (JIT) compilation to fuse query operators of the same pipeline into a monolithic code fragment. Although the authors of [9] call JIT as a data-centric compilation, the query execution is still computing-centric by moving data to the CPU with many adaptations to make better use of the CPU pipeline. In this thesis, we investigate the data-centric model to tackle the data movement problem in query execution systems with logical units integrated closer to the data (inside memory devices), which is called Processing-in-Memory (PIM) [10].

Database engineers have been evaluating PIM approaches with processing components installed in magnetic disks [11, 12, 13], RAM [14], and more recently in flash disks [15, 16, 17]. However, commercial products have not been adopting those approaches for three main reasons: 1) Limitations of the hardware technology; 2) The continuous growth in CPU performance complied to the Moore's Law and Dennard scaling<sup>1</sup>; 3) The lack of a general programming interface that leads to low abstraction level when handling hardware errors.

<sup>&</sup>lt;sup>1</sup>The Dennard scaling has a parallel to Moore's law in terms of energy consumption. In 1974, Robert H. Dennard et al. postulated that transistor areas get smaller as their power density stays constant.

Recently, PIM architectures came back to the spotlight due to the introduction of Through-Silicon Vias (TSVs). The TSV enables the integration of DRAM dies and logic cells in the same chip area, forming a 3D-stacked memory. Current commercial GPUs already embed the emerging 3D-stacked memories, such as the Hybrid Memory Cube (HMC) [18] and the High Bandwidth Memory (HBM) [19]. However, there has not been any in-depth study of query execution on PIM with SIMD support.

#### 1.1 THE PROBLEM

Modern query execution systems have relied on computing-centric architecture to process database operators. They were designed to extract the best features of modern CPUs (e.g., CPU pipeline and out-of-order instruction execution) and of the caching mechanism. The major downside of those designs is the data movement throughout the memory hierarchy. Data still need to be transferred from memory to the processor within the CPU, which severely degrades performance and requires much energy during data transferring. For instance, in Online Analytical Processing (OLAP), the data movement to validate filters in long-running queries accounts for 40 - 80% of the execution time in resource stalls, memory stalls, and branch mispredictions [20]. A recent study of the Google's workloads [1] demonstrated that 62.7% of the total system energy spent is due to data movement. This study also presents the potential of PIM reducing around 55% of energy and execution time, on average.

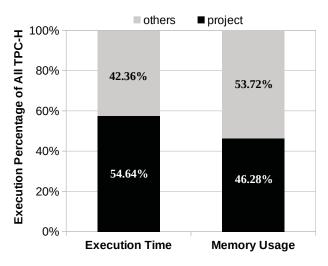

In this thesis, we investigate the impact of data movement of query execution in modern relational DBMS. Figure 1.1 presents the execution time and memory usage when executing the 100 GB TPC-H data analysis benchmark [21] in the MonetDB [22] DBMS<sup>2</sup>. This result highlights the data movement problem that we face in today's DBMS.

Figure 1.1: The impact of data movement on MonetDB.

<sup>&</sup>lt;sup>2</sup>The TPC-H is the standard query execution benchmark for data analysis. Further details of the experiment design are presented in Chapter 5.

We highlight the projection operator and include the other operators into the category "others". Just the projection operator is responsible for almost 55% of execution time. The projection operator takes the burden of tuple reconstruction and the materialization of intermediate results with direct impact in data movement with more than 46% of the memory usage compared to all the other query operators. These results are mainly caused by moving data throughout the memory hierarchy. Notice that the other operators also move data around the memory hierarchy as a direct impact of the computing-centric architecture design of the materialization query execution system of MonetDB (also implemented in VoltDB). As we will show in this thesis, this impact is not restricted to the materialized query execution as we also observed in all the other query execution models: vectorized (e.g., SQLServer, VectorWise, Hyrise, DB2) and pipelined (e.g., PostgreSQL, DB2, Oracle, MySQL, SQLite).

#### 1.2 MOTIVATION

The recent trend of PIM promises to tackle the memory and energy wall problems lurking in the data movement around the memory hierarchy. Naturally, we investigate the performance of query operators running on modern PIM as a kickoff to unravel potential advantages and drawbacks. For instance, we evaluated the projection operator and a naive implementation of the join operator (i.e., the Nested Loop Join (NLJ)) in Chapter 7. The preliminary results show distinct performances for both operators. While the projection operator reaches a significant improvement on PIM (almost  $6 \times$  faster than the x86 processor), the NLJ has an intricate result with better performances on x86 processing.

Those preliminary results point out that the decision to execute database operators on PIM is not trivial. The traditional x86 computing-centric model still has beneficial properties, and there are several opportunities for energy savings with PIM execution. Also, the query execution systems have many operators with a myriad of algorithm implementations. Besides, dataset characteristics (e.g., size and cardinality) shall interfere with the performance of the database operators on each architecture. In this thesis, we investigate *how modern DBMS can embrace PIM in query execution*.

#### **1.3 HYPOTHESIS**

To alleviate the data movement problem on modern database systems, we formulate the following hypothesis:

New PIM devices shall mitigate the data movement in Query Execution System, and thus reduce execution time and energy consumption.

#### 1.4 CONTRIBUTIONS

This thesis reveals the importance of rethinking the query execution systems for emergent PIM architectures. We rely on our hypothesis to investigate the following research questions with the specific contributions listed:

- 1. What is the potential reduction in data movement that PIM devices can provide on query execution systems?

- We present an investigation of near-data processing approaches on memory devices (e.g., hard disks, flash disks, and main memory). Our goal is to extract some learning of how query execution systems were evaluated over the years (Chapter 3).

- We explore the selection operator (for its simplicity and relevance) using current PIM capabilities (Chapter 4).

This work is completed and was published in ADMS@VLDB<sub>2018</sub> [23].

- 2. Which is the most relevant group of query operators to evaluate on PIM?

- We present a study of the most time and memory consuming database operators on MonetDB (Chapter 5).

- We detail the implementation of query operators on PIM hardware with SIMD support (Chapter 6).

- We design a new SIMD sorting algorithm to take advantage of SIMD capabilities on x86 (using AVX512 extensions) and PIM devices (Chapter 6).

This work is completed and was published in PVLDB<sub>2019</sub> [24].

- 3. What are the relevant characteristics that impact the decision between PIM and x86 processing?

- We present a comprehensive performance analysis of the query operators on modern PIM hardware and the traditional x86-style processing regarding the effect of data movement around memory (Chapter 7).

- We distinguish the trade-offs to process each SIMD operator on top of the materialized, vectorized, and pipelined query execution models (Chapter 7).

This work is completed and was published in PVLDB<sub>2019</sub> [24].

- 4. How can DBMSs coordinate intra-query execution between the CPU and PIM to exploit the potential benefits of each architecture?

- We propose a classification method based on operator profiles to decide in which architecture to process each operator (Chapter 8).

- We design a PIM-aware query scheduler to exploit the potential of hybrid scheduling of database operators, which interleaves the execution between PIM and x86 processing (Chapter 8).

- We provide heuristics to build a hybrid query plan and discuss the experimental results. Our hybrid scheduler reduced execution time by 35% and 45% when compared to PIM and x86 hardware-specific query plans, respectively. The hybrid scheduler reduced energy consumption by more than 2× compared to the traditional x86 processor (Chapter 8).

- We introduce a new hybrid PIM-x86 SIMD query execution system that brings new challenges and opportunities (Chapter 8).

This work is completed and was published in PhD@VLDB<sub>2018</sub> [25], SBBD<sub>2019</sub> [26], and DEXA<sub>2019</sub> [27].

#### 1.5 ORGANIZATION

The remainder of this thesis is organized as follows. Chapter 2 presents an overview of the architecture of DBMSs and the main query execution models. Chapter 3 presents related work on near-data processing in memory devices. Chapter 4 gives an overview of the new PIM architectures. Chapter 5 delivers our experiment design and introduces the simulator used to evaluate the baseline PIM architecture. Chapter 6 details the SIMD instructions used in the implementation of the database operators. Chapter 7 presents results and analysis of the execution of operators on PIM and x86 architectures. We also evaluate the performance and energy consumption of the distinct query execution model. Chapter 8 introduces the hybrid PIM-x86 SIMD query execution system with results for a hybrid PIM-x86 query scheduler. Chapter 9 discusses the main conclusions of this thesis.

#### **2** DATABASE FOUNDATIONS

In this chapter, we present the foundations of relational databases and detail the modules in which this thesis takes place. A relational database is a collection of related data stored in tabular data structures corresponding to real-world entities (or rows) and their attributes (or columns). There is a distinction between the logical and physical representation of database tables, called "Data Independence"<sup>1</sup>. At a logical level, we are concerned with the conceptual schema of an application and user views. At a physical level, database tables need to be mapped onto one dimensional structures before being stored: rows-by-rows (or row-store) and/or column-by-column (or column-store). Although this thesis focuses on the physical level, more specifically on how to retrieve relational data from modern memory hardware, we need to discuss the fundamental relational operations that come from the model designed at the logical level.

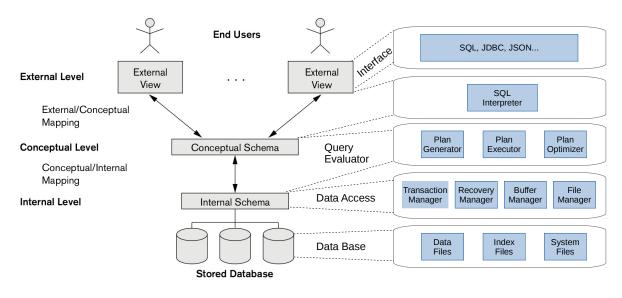

The DBMS is a collection of programs that enables the distinction between logical and physical levels, and provides a way to store and retrieve database information [28]. We begin with an overview of the "Three-schema arquiteture" of DBMS that separates the logical and physical database levels, depicted by Figure 2.1. On the left, there is a schema in three layers: the external, the conceptual, and the internal levels. On the right, the diagram shows the main components of a DBMS. The external interface (e.g., Structured Query Language (SQL)) receives commands for data recovery and the SQL Interpreter transforms them to an internal representation. The *Query Evaluator* generates candidate query plans and chooses one to be executed. During query execution, the *Data Access* module manages the data access recovering data from internal structures in the *Database* layer.

Figure 2.1: A general architecture of a DBMS [28, 29].

<sup>&</sup>lt;sup>1</sup>"Data Independence" is also defined by [28] *as the capacity to change the schema at one level of a database system without having to change the schema at the next higher level.*

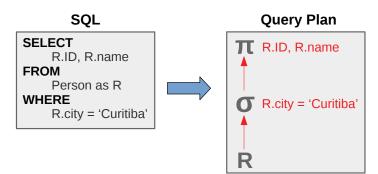

Now, we briefly describe the execution of SQL queries in the DBMS. Further details in the execution of queries are left to the sections of query execution models. Query processing starts with the submission of an SQL query to the DBMS. The *SQL Interpreter* validates the query in lexical, syntactic, and semantic aspects. After the query validation, the *Query Evaluator* generates logical query plans based on the relational algebra. The *Plan Optimizer* chooses the best-estimated plan to be executed and transforms the logical plan into a physical execution plan. The physical plan consists of primitives (functions and algorithms) and dataset information (e.g., indexes, files, and columns) needed to run the plan. Figure 2.2 presents an SQL query and its corresponding query plan from the relational algebra.

Figure 2.2: An SQL query and its corresponding query plan.

The *Plan Executor* processes the query from the physical plan. The query scheduler (within the Plan Executor) orchestrates the execution of primitives, ordering them, selecting the input dataset, storing intermediate data, and synchronizing the execution among primitives. During the physical plan execution, the scheduler communicates with the *Data Access* layer, consulting the *Buffer Manager* and *File Manager* components. The Buffer Manager contains information about the pages in memory and their addresses. When needed to access data in secondary memory, the File Manager is responsible for that extraction.

As our thesis investigate the execution of queries to retrieve relational data stored in modern PIM hardware, in the next sections, we next expose the relational model, the operators of the relational algebra, and the distinct storage layouts. We finish with the query execution models.

#### 2.1 RELATIONAL MODEL

The relational model proposed by Edgar F. Codd [30] represents databases as a set of relations, which is the conceptual schema of Figure 2.1 and the internal level are the data structures to store the relations. A relation is abstracted to a table and the columns to attributes of the relation. Thereby, a row in the table is a collection of values that can represent an instance of a relation or a relationship. Formally in the relational model, a row is called a tuple (t), a column is an attribute (A), and a table is defined as a relation (R). Each attribute belongs to an specific domain (D), commonly assigned to a data type.

A schema of the relation *R* is denoted by  $R(A_1, A_2, ..., A_n)$ , such that *R* is the name of the relation followed by a list of attributes  $A_1, A_2, ..., A_n$ . Each attribute  $A_i$  has a defined domain as  $dom(A_i)$ .

An instance *r* from the schema  $R(A_1, A_2, ..., A_n)$  is denoted by r(R), which is a state of the schema. r(R) is comprised by a set of tuples  $r = \{t_1, t_2, ..., t_m\}$  and the quantity of tuples is defined as |R|. A tuple consists of a sequential list of *n* values  $t = \{< v_1, v_2, ..., v_n >\}$ , each value  $v_i$  belongs to  $dom(A_i)$ . The i-th value  $(A_i)$  of a tuple is denoted as  $t.A_i$  or t[i].

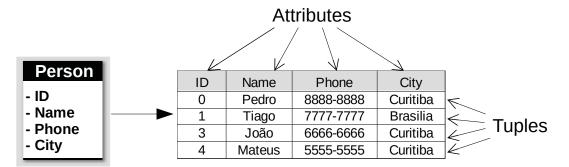

For example, let us consider the entity Person with four attributes: ID, Name, Phone, and City. The relational schema for that entity is Person(ID, Name, Phone, City), which contains the name of the relation (Person) and the four attributes. An instance of this schema with four tuples is represented bellow:

$$r = \{ < 0, Pedro, 888888888, Curitiba >,$$

(2.1)

$$< 1, Tiago, 77777777, Brasilia >,$$

(2.2)

$$< 3, Joo, 666666666, Curitiba >,$$

(2.3)

$$< 4, Mateus, 55555555, Curitiba > \}$$

(2.4)

Figure 2.3 illustrates that relation schema. Considering the tuple  $t_1 = <0$ , *Pedro*, 8888-8888, *Curitiba* >, to access the fourth value (*A*<sub>4</sub>):  $t_1.A_4 \equiv t_1[4] = Curitiba$ .

Figure 2.3: The entity Person and an instance of its respective relational schema.

#### 2.2 RELATIONAL ALGEBRA

The relational algebra is a formal language for retrieving data from the relational model, which consists of a basic set of operations that allows the user to specify queries using expressions. An operation produces a new relation as an entry to another one. A chain of operations in relational algebra forms an expression in which the output is also a new relation. Although the expression is unique, other ones can generate the same resulting relation, i.e., there

are many options to reach the same result. Based on this principle, DBMSs create different query plans to optimize data recovery.

The relational algebra is based on the set theory, since each relation is defined as a set of tuples  $(r = \{t_1, t_2, ..., t_m\})$ . Consequently, it has the following operations inherited from set theory: union, intersection, difference set, and cartesian product. Other operations were also added to relational databases, such as selection, projection, and join. These operations are associated with operators in SQL queries.

#### 2.2.1 Selection Operation

In relational algebra, the selection operation ( $\sigma_{}(R)$ ) selects a subset of the original relation (R) according to a condition. The resulting subset is a new relationship with the number of tuples  $|\sigma_{\langle p \rangle}(R)| \leq |R|$ . The selection condition is also known as a predicate  $|\langle p \rangle$  that is a boolean expression [28] composed by clauses of the form:

- <attribute name> <operator of comparison> <constant value>, or

- <attribute name> <operator of comparison> <attribute name>

Such that *<attribute name>* is an attribute of *R*, *<operator of comparison>* is one of the operators:  $\{=, <, \leq, >, \geq, \neq\}$  and *<constant value>* is a constant belonging to the domain of the attribute. Boolean operators (e.g., AND, OR, and NOT) connect multiple predicates to form a generic selection condition.

The following is an example of applying the selection operation on the relational schema of Figure 2.3 and the selection condition filters the PERSON whose name is Tiago. Code 2.1 presents that selection operation, which corresponds to the WHERE clause of the SQL in Code 2.2. SELECT \*

1

3

$\sigma_{Name=Tiago}$  (Person)

2

Listing 2.1: Example of Selection.

2 FROM Person WHERE Name = "Tiago"

Listing 2.2: Selection in a SQL query.

It is important to note that selection is a commutative operation, i.e.:

$$\sigma_{< p_1 >} (\sigma_{< p_2 >} (R)) = \sigma_{< p_2 >} (\sigma_{< p_1 >} (R))$$

Therefore, multiple selections on the same relation shall be grouped into a single operation and the predicates combined through the conjunction operator (AND), such that:

$$\sigma_{< p_1 >} (\sigma_{< p_2 >} (... (\sigma_{< p_n >} (R)...) = \sigma_{< p_1 > AND < p_2 > AND... < p_n >} (R)$$

The projection operation of the relational algebra picks a subset of attributes from a relation (R), forming a new relation with only those attributes and their values. This operation corresponds to the following general form:

$$\Pi_{< attribute \ list>}(R)$$

$\Pi$  is the symbol to denote the projection operator, <attribute list> is a subset of attributes contained in R. Code 2.3 presents an example of the projection operation, which corresponds to the SELECT command in SQL, as exemplified by Code 2.4. This is an example of applying the projection operation to the relational schema of Figure 2.3, where the names and cities are projected from the relation Person.

$\Pi_{Name,City}$  (Person)

1

2

1

2

Listing 2.3: Example of Projectin.

SELECT Name, City

FROM Person

Listing 2.4: Projection in a SQL query.

Multiple projection operations on the same relation can be abbreviated, once the attribute list of one projection is contained in another one, i.e.:

$$\Pi_{}$$

$(\Pi_{}$   $(R)) = \Pi_{}$   $(R)$ , if and only if,  $} \subseteq$

Usually, the selection and projection operations occur together in expressions of the relational algebra and SQL queries, as exemplified in Codes 2.5 and 2.6. In addition, it is possible to perform some aggregations together with projections, such as MIN, MAX, SUM, AVG, COUNT, arithmetic operations (+, -, \*, /) etc.

$\Pi_{Name,City} (\sigma_{Name=Tiago} (Person))$

Listing 2.5: Example of Projection and Seletion together.

|  | SELECT | Name, | City |

|--|--------|-------|------|

|--|--------|-------|------|

- 2 FROM Person

- **3 WHERE name = "Tiago"**

#### 2.2.3 Join Operation

Join is a binary operation that combines tuples of two relations into a single one. It establishes the relationship between relations by comparing the join attributes and generating a set of tuples that match these attributes.

The general formula to join two relations  $R(A_1, A_2, ..., A_n)$  and  $S(B_1, B_2, ..., B_m)$  is:

$$R \bowtie_{< join \ condition>} S$$

Listing 2.6: Projection and Selection in a SQL query.

The result of the join operation is a new relation Q with the tuples that satisfy the join condition. The tuples of this relation are formed by the concatenation of tuples in R and S,  $Q(A_1, A_2, ..., A_n, B_1, B_2, ..., B_m)$ , in this order, such that Q contains n + m attributes. When performing the join operation, as the join condition is satisfied, the tuple of R is matched with the corresponding tuple in S. Multiple join conditions are connected through conjunctions:

<*condition*1> *AND* <*condition*2> *AND* ... *AND* <*condition*N>, a condition is a predicate of the form  $A_i \ \theta \ B_j$ , such that  $A_i$  is an attribute of *R* and  $B_j$  is an attribute of *S*, and  $\theta$  is an of the comparison operators:  $\{<, \leq, >, \geq, =, \neq\}$ .

To exemplify this operation, let us consider the relation Employee (Person\_ID, Salary) that contains employee information for a company, which relates to the Person relation. Code 2.7 and Code 2.8 present the join expression and the SQL query, respectively. Table 2.1 exemplifies the result of the operation.

| - |  |

|---|--|

|   |  |

| 2 |  |

| Person | $\bowtie_{ID} = ID\_Person$ | Employee |

|--------|-----------------------------|----------|

|--------|-----------------------------|----------|

| Listing | 2.7: | Exampl | le | of | Join. |

|---------|------|--------|----|----|-------|

|---------|------|--------|----|----|-------|

| SEL | ECT * |

|-----|-------|

|-----|-------|

2 FROM Person JOIN Employee

ON ID=ID\_Person

Listing 2.8: Join in a SQL query.

| ID | Name   | Phone     | City     | ID_Person | Salary      |

|----|--------|-----------|----------|-----------|-------------|

| 0  | Pedro  | 8888-8888 | Curitiba | 0         | \$2.000,00  |

| 1  | Tiago  | 7777-7777 | Brasília | 1         | \$15.000,00 |

| 2  | João   | 6666-6666 | Curitiba | 2         | \$5.000,00  |

| 3  | Mateus | 5555-5555 | Curitiba | 3         | \$3.500,00  |

Table 2.1: The join of the relations Person and Employee.

#### 2.3 STORAGE LAYOUT

The storage layout is a fundamental component of a DBMS (within the DataBase layer, see Figure 2.1). Studies [31] have pointed out that the way data are arranged directly influences the query processing. In a nutshell, a table can be stored by its rows or columns. The row-store layout (also called linear or row-by-row layout) stores rows contiguously in the data files. This means that a row is entirely stored in a file and read from a file. The column-store layout (also called columnar or column-by-column layout) stores columns contiguously in the data files. This means that a row is partitioned by its columns that are entirely stored in a file and read from a file.

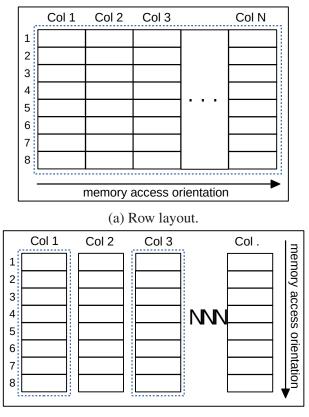

Figure 2.4 depicts the row-store and column-store layouts. To access two columns, e.g., columns *Col*1 and *Col*3, a column-store system straight load the required columns from memory (the dashed lines in Figure 2.4(b) may represent a file or a data structure with each column stored separately). At the same time, a row-oriented system has to load the full row with many useless columns (the dashed lines in Figure 2.4(a)), wasting memory throughput. As observed in

Figure 2.4 and demonstrated by Abadi D. et al. [32] the row-store layout is suitable for Online Analytical Processing (OLTP) workloads, because transactions are written to disk without any row partitioning with low input/output operation overhead. In contrast, the column-store needs to partition each column from a row to different data structures with high input/output operation overhead. However, the columnar layout is suitable for OLAP, because complex queries fetch from disk only the required columns without wasting memory throughput. Although we briefly describe both storage layouts in the following sections, this thesis focuses on the column-store that is the layout of choice of large-scale OLAP applications of contemporary BigData systems.

(b) Column layout.

Figure 2.4: Row vs. Columnar layout. The arrows show the data access orientation, and the dashed blue lines depict the access to two columns on both layouts.

#### 2.3.1 Row-Store Layout

The row-store layout in the relational model is defined as follow:

*Linear*  $\rightarrow$  *r* = ( $t_1, t_2, ..., t_m$ ), *r* is an instance of a relation and  $t_i$  is a tuple with *n* values:  $t_i = \langle v_1 \Rightarrow v_2 \Rightarrow ... \Rightarrow v_n \rangle$ , such that  $v_j \Rightarrow v_{j+1}$  means that the values of a tuple are stored continuously (adjacent),  $\forall j \mid 1 < j < n$ . Therefore, the j-th value of a tuple is accessed by *r*. $t_i[j]$ and, consequently, the next value *r*. $t_i[j+1]$  will be adjacent in memory.

The DBMS applies the *N*-ary Storage Model (NSM) [33] for physical storage, which divides the relation (table) into blocks, storing row-by-row. Thus each row contains all its columns (values) contiguously arranged in memory.

This arrangement requires a few memory operations to read an entire tuple from memory, case  $|t_i|$  is less than or equal to one cache line, all values of a tuple will be on the same cache line. As the values of a tuple (see Section 2.1) represent an instance of an entity, the row-store layout has proven conducive to workloads that require information at the entity granularity. Therefore, row-oriented systems can fetch all information of an entity, update and even remove it efficiently using a few read and/or write memory operations. This behavior is characteristic of OLTP workloads.

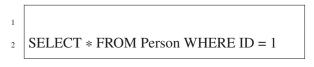

Let us consider the SQL Code 2.9 that selects the information of the Person which *ID* is 1. In the row-store layout, just a single memory read operation is enough to obtain all information to that person, as Figure 2.5 depicts on the dashed line.

Listing 2.9: A OLTP query.

| Linear Layout      |        |           |          |  |  |  |

|--------------------|--------|-----------|----------|--|--|--|

| ID Name Phone City |        |           |          |  |  |  |

| 0                  | Pedro  | 8888-8888 | Curitiba |  |  |  |

| 1                  | Tiago  | 7777-7777 | Brasilia |  |  |  |

| 3                  | João   | 6666-6666 | Curitiba |  |  |  |

| 4                  | Mateus | 5555-5555 | Curitiba |  |  |  |

Figure 2.5: OLTP query on the row-store layout.

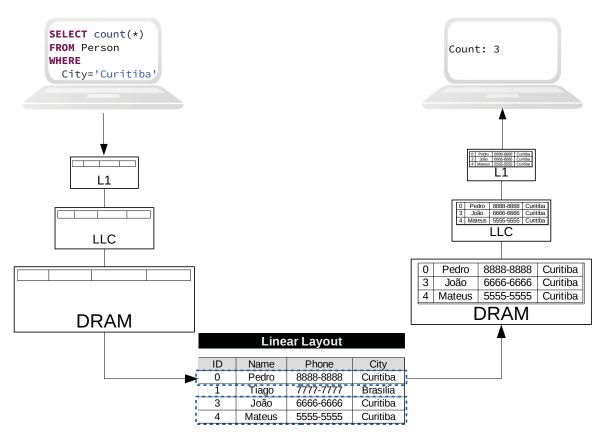

On the other hand, the row-store layout is not suitable for OLAP workloads. Analytics queries require to access a few columns. Using that layout, however, many memory operations are wasted when accessing useless columns for the query, augmenting data movement. Considering the OLAP query in the left side of Figure 2.6, it selects the tuples in which the *City* column is equal to "Curitiba" and computes the total. This query reads all the columns of the table (see Figure 2.6, dashed lines), loading into the memory hierarchy the unneeded columns: *ID*, *Name*, and *Phone*, but the query just requires the *City* column.

#### 2.3.2 Colum-Store Layout

The column-store layout in the relational model is defined as follow:

*Columnar*  $\rightarrow$  *r* = (*t*<sub>1</sub>,*t*<sub>2</sub>,...,*t<sub>m</sub>*), *r* is an instance of a relation and *t<sub>i</sub>* is a tuple with *n* values:  $t_i = \langle v_1 \iff v_2 \iff \dots \iff v_n \rangle$ , such that  $v_j \iff v_{j+1}$  means that the values of a tuple are **not** stored continuously (adjacent) in memory,  $\forall j \mid 1 < j < n$ . In contrast, values from the same column are stored contiguously, i.e.,  $t_i[j] \Rightarrow t_{i+1}[j], \forall t_i \mid 1 < i < m$ .

Therefore, we define a relation instance in the columnar layout as follow:

Columnar  $\rightarrow r = (C_1, C_2, ..., C_n)$ , *n* is the degree of the relation, a  $C_i$  is a column that contains all values for the attribute  $A_i$ . The columns are stored separately, values within the same column are adjacent and arrange according with the order of its tuples. The i-th value of a tuple  $t_j$  is accessed by  $C_i[j]$ , such that  $C_i[j] \Rightarrow C_i[j+1]$  are coalescing values,  $\forall j \mid 1 < j < m$ . Thus, the j-th tuple is defined as  $t_j = (C_1[j], C_2[j], ..., C_n[j])$ .

The columnar layout is inspired on the *Decomposition Storage Model* (DSM) [34], which vertically partitions the tables, then each column is stored separately, as depicted in

Figure 2.6: OLAP query on the *row-store* layout.

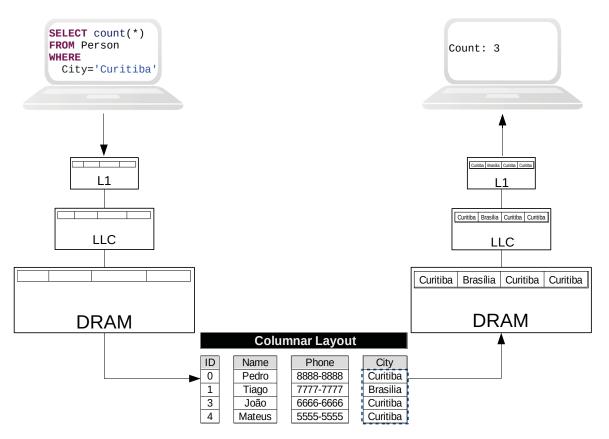

Figure 2.4(b). Thefore, OLAP queries take advantages of this layout by loading from memory only the required columns. Figure 2.7 illustrates the behavior of OLAP queries on the columnar layout, then just the column *City* is load from memory, saving memory throughput and energy.

Figure 2.7: OLAP query on the *columnar* layout.

#### 2.4 QUERY EXECUTION MODELS

This section introduces the current query execution models implemented as the query execution subsystem in modern DBMSs. In [35], Daniel J. Abadi describes four main properties of OLAP workloads that can be used to guide the implementation of a query execution system. They are: (1) **unpredictable**, OLAP queries tend to be more exploratory in nature rather than defined to specific business tasks, as transactions; (2) **longer lasting**, OLAP queries may execute in hours moving large volumes of data in contrast to transactions that are expected to execute in milliseconds with small amount of data; (3) **read-mostly**, OLAP queries are more Read-Oriented than Write-Oriented. Typically, only batch writes are executed in OLAP databases; and (4) **attribute focused**, OLAP queries are meant to process summaries of lots of entities (or rows). In this case, summaries aggregate records of a few number of columns.

Next, we describe the Volcano query execution model, followed by the materialization, vectorized, and pipelined model.

#### 2.4.1 The Volcano Query Execution Model

Most of the query execution systems have relied on the iterator model implemented in the Volcano system [36], like in PostgreSQL, MySQL and SQLite DBMSs. In this model, operators in a query plan exchange tuples through a standard iterator interface with the *open*, *next*, and *close* procedures in a producer and consumer design way, also called tuple-at-a-time processing. This interface isolates the operators, and thus each one manages all issues of control, internally.

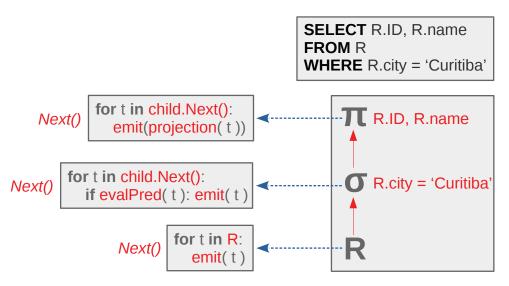

Figure 2.8 shows the iteration model in the execution of a query (see Listing 2.10). Each operator in a query tree emits tuples to the next operator, which consumes a tuple through the invocation of the *next* procedure. Coalescing operators in a query tree exchange data (tuples) through a shared buffer (queue), the producer operator pushes data into the buffer for a pull consumer. The DBMS uses a semaphore to synchronize such exchanging. In OLAP, the Volcano-like tuple-at-a-time execution incurs in a high runtime interpretation overhead and waste of memory throughput by loading the entire tuple, even useless columns [37, 32].

| Listing 2.10: | Simple SQL | query statemer | t with two | projections | and | one selection | operations |

|---------------|------------|----------------|------------|-------------|-----|---------------|------------|

|---------------|------------|----------------|------------|-------------|-----|---------------|------------|

```

1 SELECT

2 R.ID, R.name

3 FROM

4 R

5 WHERE

6 R.city = 'Curitiba';

```

Figure 2.8: Volcano iterator model to the left and the query execution tree to the right (i.e. query plan).

#### 2.4.2 The Materialization Query Execution Model

The volcano-style systems have many downsides for query processing when modern DBMS implement the column-store layout for OLAP (see [32] for a detailed discussion). An alternative is the materialization query execution model implemented by the MonetDB [38] and C-Store [39, 40] DBMSs. The materialization query execution is designed to benefit from the column-store layout and consequently favor OLAP workloads. This model performs column-at-a-time processing as it only moves the required columns around memory to execute a query saving a great deal of memory throughput.

Although modern column-oriented DBMS improve the execution of analytic queries, they undergo the tuple reconstruction problem [41]. Every time a given column is fetched, these systems must perform a tuple reconstruction action based on a temporary data structure (which is the result of a previous operator in a query plan). The *projection* and *projectionpath* physical operators take the burden of the tuple reconstruction or the materialization of intermediate results. They are invoked multiple times within a query plan, e.g., case a query requires N columns, at least N - 1 projections have to be performed. Therefore, they implement the following temporary data structures to hold intermediate results: selection vector, position vector, and bitmap.

The execution model processes each query operator to completion over its entire input data in a column-at-a-time manner. One operator finishes before any invocation of a subsequent data-dependent operator. Also, it demands the late materialization strategy to delay the reconstruction of tuples until it is necessary to continue executing the query [6].

To demonstrate how the materialization query execution model operates, we run a small piece of the TPC-H Query 03 in MonetDB, see Listing 2.11. This piece implements five filter predicates (*WHERE* clause) from three different tables (*customer*, *orders*, and *lineitem*) to project the  $l\_discount$  column.

Listing 2.11: Small piece of the TPC-H Query 03.

```

SELECT

1

l discount

2

FROM

3

customer,

4

orders,

5

lineitem

6

WHERE

7

c_mktseqment = 'BUILDING'

8

and c_custkey = o_custkey

9

and l_orderkey = o_orderkey

10

and o_orderdate < date '1995-03-15'

11

and l_shipdate > date '1995-03-15'

12

```

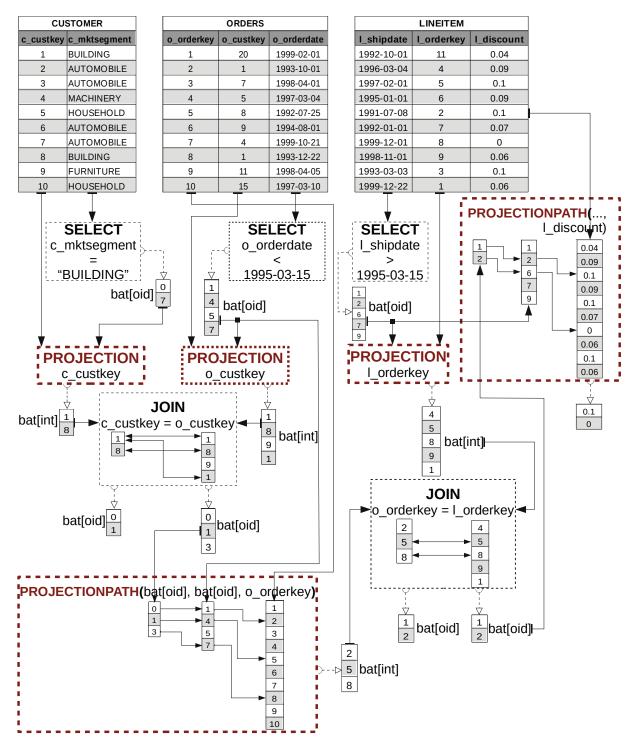

We enabled the SQL *trace* statement of MonetDB on the query to record every primitive of MonetDB Assembly Language (MAL). Figure 2.9 presents a top-down diagram of the execution plan from that query and highlights the projection operators (*projection* and *projectionpath*). The query plan optimizer pushes down the selections to filter tree columns:  $c_mktsegment$ ,  $o_orderdate$ , and  $l_shipdate$ . Each selection operator emits as output a Binary Association Table (BAT) [42] of OIDs<sup>2</sup>, i.e., a selection vector with the positions that matched the filter predicates as exemplified by Listing 2.12, which applies the branch boolean calculation technique to avoid branch misprediction [43].

Listing 2.12: Selection code example.

```

void select(int n, int *col, int filter, int *res) {

for (size_t i,j=0; i < n; ++i) {

/* boolean calculation, branchless code */

bool b = test_filter(col[i], filter);

j += b;

res[j] = i; }

</pre>

```

Projections use those intermediate selection vectors to materialize the join columns:  $c\_custkey$ ,  $o\_custkey$ , and  $l\_orderkey$ , i.e., they filter an input column based on the selection vector, for instance, the Listing 2.13.

| Listing 2.13: | Projection | code | example. |

|---------------|------------|------|----------|

|---------------|------------|------|----------|

```

void projection(int n, int *sel_vec, int *col, int *res) {

for (int i=0; i < n; ++i) {

int pos = sel_vec[i];

res[i] = col[pos]; }

}</pre>

```

<sup>2</sup>OID is the object ID, i.e., it is an ID number assigned to a certain position in the table.

The query plan, in some points, requires to materialize columns that depend on two or more position vectors. In these points, the *projectionpath* primitive is invoked to glue distinct position vectors and then to project a target column. For instance, in Figure 2.9, two *projectionpath* primitives join position vectors generated by selection and join operators. The first one glues two position vectors: the one generated by the selection on column *o\_orderdate* and another from the join of the *custkeys* (*c\_custkey* and *o\_custkey*). It traverses the vectors to project the mapped values from the column *o\_orderkey*. Listing 2.14 exemplifies as the *projectionpath* behaves. Firstly, it traverses the small position vector, e.g., *pos\_vec*1, and uses it to filter the second one (*pos\_vec*2), then only the filtered values are materialized from the target column.

Listing 2.14: Projectionpath code example.

The diagram in Figure 2.9 illustrates the interaction of database operators in a query plan. Furthermore, it discloses details of how tuple reconstruction materializes within a materialization query execution model, and thus the relevance of the projection operations on it. Although these systems mitigate data movement by processing column-at-a-time and avoiding memory throughput waste such as in row-oriented systems, they have to maintain several intermediate data structures (e.g., selection vector or bitmap) in memory. Moreover, they materialize many intermediate columns during query execution.

### 2.4.3 The Vectorized Query Execution Model

The vectorized query execution model tries to avoid some pitfalls of the Volcanolike iterator model. The tuple-at-a-time execution of Volcano-style causes high interpretation overhead and inhibits compilers to exploit CPU parallelism, leading DBMSs to low Instructions per Cycle (IPC), e.g., IPC of 0.7 [8].

The Volcano iterator model allows high cohesion and low coupling by encapsulating database operators. However, it performs pipelined processing among database operations using the tuple-at-a-time execution: Every database primitive<sup>3</sup> is called multiple times during a query execution at a tuple granularity. It means that one singular operation (e.g., an arithmetic operation) is invoked for every singular value that it should process.

<sup>&</sup>lt;sup>3</sup>A database primitive is one physical compiled function/routine that the DBMS calls during the query execution.

Considering, for instance, the sum expression: +(double src1, double src1) : double, which sum two double values, in which src1 could be a value from one column and src2 either a value from another column or one constant value. The assembly-like code would look like:

Listing 2.15: Sum of two double values in an assembly-like code.

| LOAD  | src1, | regl  |      |

|-------|-------|-------|------|

| LOAD  | src2, | reg2  |      |

| ADD   | regl, | reg2, | reg3 |

| STORE | dst,  | reg3  |      |

The pitfalls of this code are the inherent data hazards (data dependence): one between the LOADs and the ADD instruction and another between the ADD and STORE. In the first one, the ADD instruction must wait for the completion of the LOADs to continue the CPU pipeline. The STORE instruction depends on the result of the addition to save it into the memory. Without those dependencies, a MIPS [44] processor with only one pipeline should have an IPC of 1 (one instruction per cycle). However, the CPU must add at least two "STALL"<sup>4</sup> instructions into the pipeline to delay the execution of the ADD and another before the STORE instruction, leading to an IPC of 0.66 (0.66 = 4/6: 4 useful instructions (LOADs, ADD, and STORE) divided by the total of instructions (useful instructions plus STALLs)). This is a clear decline in CPU performance that applications must be aware.

At the same time, compilers easily solve data dependencies by putting more instructions into the pipeline, i.e., they apply the *loop pipelining/loop unrolling* technique. However, primitives in legacy DBMS compute only one operation per call, which prevents compilers to perform the loop pipelining.

The consequences of tuple-at-a-time processing are twofold: 1) Database primitives perform one operation per call, precluding compilers to make a pipelined loop; 2) The high cost of primitive call for every single operation.

Those drawbacks lead to the vector processing of database primitives introduced in MonetDB/X100 [7], which later let to the Vectorwise spin-off [45, 46] and many other DBMSs, including SQLServer [47] and DB2 BLU [48]. These DBMSs conceive the vectorized processing query system. They yet employ the Volcano-like pipelined processing, but instead of tuple-at-a-time execution, they operate at the granularity of vectors. These vectors have a small size (e.g., 1024 values) to fit into the caches, and thus database primitives should be cache-conscious by processing large datasets in cache-chunk fragments. Vectorized primitives allow compilers to generate efficient loop-pipelined code.

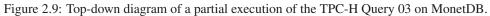

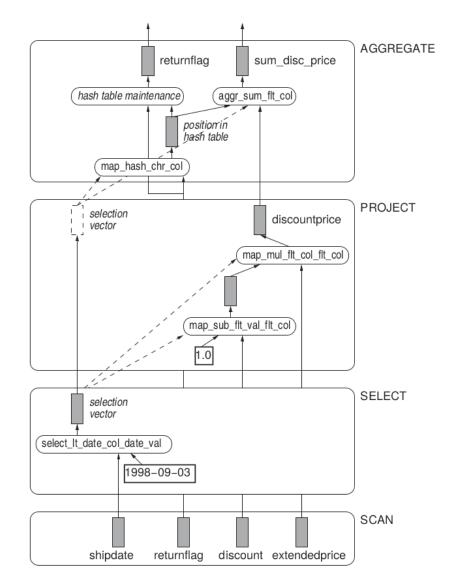

Let us consider the simplified version of TPC-H Query 01, in Listing 2.16. This query filters the column  $l\_shipdate$  and generates a selection vector, then it applies a subtraction on column  $l\_discount$ , and right after a multiplication with column  $l\_extended price$ , the result  $(sum\_disc\_price)$  is aggregated based on the  $l\_returnflag$  column.

<sup>&</sup>lt;sup>4</sup>STALL is an useless instruction to delay the execution of the pipeline until a certain value is ready, it is also called a **bubble** or **NOP** ("no operation") instruction.

```

Listing 2.16: Simplified version of TPC-H Query 01.

```

```

SELECT

1

l returnflag,

2

sum(l_extendedprice * (1 - l_discount)) as sum_disc_price

3

FROM

4

lineitem

5

WHERE

6

l shipdate < date('1998-09-03')</pre>

7

GROUP BY

8

l_returnflag

9

```

The diagram in Figure 2.10 presents the plan execution of Query 01. Every database primitives process a vector-at-a-time. The scan operator, at the bottom of Figure 2.10, emits vector chunks to be processed by the selection operator, which generates a selection vector. Then, there are two projections with arithmetic expressions that apply the selection vector to filter the target columns and perform the subtraction or multiplication operations. The aggregation operator reads the group column ( $l_returnflag$ ), filtering it with the selection vector, calculates the hash address to load the Hash Table (HT) entries, and updates the aggregation values with the results of the projection expressions. Note that only the target columns are scanned when strictly needed, during query execution intermediate data (e.g., selection vector and the result of projections) are kept as long as possible in caches.